### WestminsterResearch

http://www.westminster.ac.uk/research/westminsterresearch

Exploiting the bulk-driven approach in CMOS analogue amplifier design

#### Yasutaka Haga

School of Electronics and Computer Science

This is an electronic version of a PhD thesis awarded by the University of Westminster. © The Author, 2011.

This is an exact reproduction of the paper copy held by the University of Westminster library.

The WestminsterResearch online digital archive at the University of Westminster aims to make the research output of the University available to a wider audience. Copyright and Moral Rights remain with the authors and/or copyright owners.

Users are permitted to download and/or print one copy for non-commercial private study or research. Further distribution and any use of material from within this archive for profit-making enterprises or for commercial gain is strictly forbidden.

Whilst further distribution of specific materials from within this archive is forbidden, you may freely distribute the URL of WestminsterResearch: (<u>http://westminsterresearch.wmin.ac.uk/</u>).

In case of abuse or copyright appearing without permission email <u>repository@westminster.ac.uk</u>

# EXPLOITING THE BULK-DRIVEN APPROACH IN CMOS ANALOGUE AMPLIFIER DESIGN

Yasutaka Haga

A thesis submitted in partial fulfilment of the requirements of the University of Westminster for the degree of Doctor of Philosophy

December 2011

## Declaration

I hereby declare that this thesis has been completed by myself and that the research documented is carried out entirely on my own. Where other sources of information have been used, they have been quoted. I have acknowledged all main sources of help.

No part of this thesis has been submitted in support of an application for any other degree.

Yasutaka Haga

## To Hiromi

For her understandings, love and support

### Acknowledgements

I am forever indebted to my advisor Professor Izzet Kale for his great guidance and support throughout the course of my PhD studies. He is the one who introduced me the bulk-driven approach when I was confused with what to work for in my MSc project. After achieving the MSc degree I was inspired to extend the study in my PhD research, however as I moved on I completely got stuck due to too many problems this design approach is having, and eventually I almost gave up the PhD because I thought that I chose the wrong subject. But Izzet was calm when I told him this feeling. He kept on advising my works and encouraging me. This thesis would not have been possible without him.

I am also grateful to my second advisor Professor Richard C. S. Morling and my research colleagues, Dr. Hashem Zare-Hoseini, Dr. Ediz Cetin, and Dr. Alper Ucar, for peer reviewing the conference papers which I published with Izzet. Their deep insights and suggestions certainly enabled me to further improve the works.

I also wish to appreciate my wonderful family in London: Koki, Emiko, Tamami, Dirk, Issei, and Sakura. Without their unending love, none would have been possible.

My final and most heartfelt acknowledgement goes to my wife Hiromi. A new novel circuit block called the BDFVF (reported in Chapter 4 of this thesis), which in result became the gateway to success in completing my research work, was born while I was

going out with her. Ever since I married her, she has kept me in a good shape with her brilliant cooking skills. Also, her patience and understandings enabled me to complete my PhD work while our friends went travelling during holiday seasons. I am indeed delighted to dedicate this thesis to her.

Yasutaka Haga

## Abstract

This thesis presents a collection of new novel techniques using the bulk-driven approach, which can lead to performance enhancement in the field of CMOS analogue amplifier design under the very low-supply voltage constraints. In this thesis, three application areas of the bulk-driven approach are focused – at the input-stage of differential pairs, at the source followers, and at the cascode devices.

For the input stage of differential pairs, this thesis proposes two new novel circuit design techniques. One of them utilises the concept of the replica-biased scheme in order to solve the non-linearity and latch-up issues, which are the potential problems that come along with the bulk-driven approach. The other proposed circuit design technique utilises the flipped voltage scheme and the Quasi-Floating Gate technique in order to achieve low-power high-speed performances, and furthermore the reversed-biased diode concept to overcome the issue of degraded input impedance characteristics that come along with the bulk-driven approach.

Applying the bulk-driven approach in source followers is a new type of circuit blocks in CMOS analogue field, in which to the author's best knowledge has not been proposed at any literatures in the past. This thesis presents the bulk-driven version of the flipped voltage followers and super source followers, which can lead to eliminating the DC level shift. Furthermore, a technique for programming the DC level shift less than the

threshold voltage of a MOSFET, which cannot be achieved by conventional types of source followers, is presented.

The effectiveness of the cascode device using the bulk-driven approach is validated by implementing it in a complete schematics design of a fully differential bulk-driven operational transcoductance amplifier (OTA). This proposal leads to solving the low-tranconductance problem of a bulk-driven differential pair, and in effect the open loop gain of the OTA exceeds 60dB using a 0.35µm CMOS technology.

The final part of this thesis provides the study result of the input capacitance of a bulkdriven buffer. To verify the use of the BSIM3 MOSFET model in the simulation for predicting the input capacitance, the measurement data of the fabricated device are compared with the post-layout simulation results.

## **List of Contents**

| eclaration                                                              | i      |

|-------------------------------------------------------------------------|--------|

| cknowledgements                                                         | iii    |

| bstract                                                                 | V      |

| ist of Contents                                                         | vii    |

| ist of Figures                                                          | xi     |

| ist of Tables                                                           | . xvii |

| ist of Acronyms                                                         | xviii  |

| ist of Symbols and Common MOSFET Equations                              | xix    |

|                                                                         | _      |

| hapter 1 Introduction                                                   |        |

| 1.1 Moore's Law and More                                                | 1      |

| 1.2 Supply Voltage Trend                                                | 3      |

| 1.3 Rail-to-Rail Analogue Voltage Buffer and the Bulk-Driven Approach   | 4      |

| 1.4 Research Objective and Thesis Outline                               | 6      |

| 1.5 List of the Author's Publications                                   | 7      |

| 1.6 Knowledge Contributions                                             | 9      |

| 1.7 Impact of this Work                                                 | 10     |

| 1.7.1 The List of "Referred" Publications                               | 10     |

| 1.7.2 The Scanned Copy of the Gold Leaf Certificate Awarded by PRIME'10 | 15     |

| hapter 2 Characterising the Bulk-Driven Approach                        | 16     |

| 2.1 The Benefit of Utilising the Bulk-Driven Approach                   | 16     |

| 2.2 Realising the Bulk-Driven Device in CMOS Technology                 | 17     |

| 2.1.1 Bulk-Driven Device Realised in N-Well CMOS Technology             | 17     |

| 2.1.2 Bulk-Driven Device Realised in Twin-Well CMOS Technology          | 19     |

| 2.3 Drawbacks Introduced with the Bulk-Driven Approach                  | 21     |

| 2.3.1 Transconductance Reduction                                        | 21     |

| 2.3.2 Transconductance Variation                                        | 22     |

| 2.3.3 Process Related                                                   | 22     |

| 2.3.4 Degraded Latch up Immunity                  | 22 |

|---------------------------------------------------|----|

| 2.3.5 Degraded Input Impedance Characteristics    | 23 |

| 2.3.6 Reduced Bandwidth                           | 25 |

| 2.3.7 Noise                                       | 26 |

| 2.3.8 New Layout Design Techniques                | 27 |

| 2.4 Chapter Conclusion                            | 27 |

| Chapter 3 Bulk-Driven Differential Pairs          | 29 |

| 3.1 Bulk-Driven Double Replica-Biased Input Stage | 31 |

| 3.1.1 Introduction                                | 31 |

| 3.1.2 Proposal                                    |    |

| 3.1.3 Simulation Results                          | 35 |

| 3.1.4 Section Conclusion                          |    |

| 3.2 Bulk-Driven Flipped Voltage Differential Pair |    |

| 3.2.1 Introduction                                |    |

| 3.2.2 Design Approach                             |    |

| 3.2.3 Proposal                                    | 42 |

| 3.2.4 Simulated Results                           | 45 |

| 3.2.5 Section Conclusion                          | 49 |

| 3.3 Chapter Conclusion                            | 50 |

| Chapter 4 Bulk-Driven Source Followers            | 51 |

| 4.1 Bulk-Driven Flipped Voltage Follower          | 52 |

| 4.1.1 Introduction                                | 52 |

| 4.1.2 Previous Essential Works                    | 53 |

| 4.1.3 Proposal                                    | 55 |

| 4.1.4 Simulated Results                           | 57 |

| 4.1.5 Section Conclusion                          | 62 |

| 4.2 Bulk-Driven Super Source Follower             | 63 |

| 4.2.1 Introduction                                | 63 |

| 4.2.2 Previous Essential Works                    | 63 |

| 4.2.3 Class-AB Bulk-Driven Super Source Follower  | 65 |

| 4.2.4 Simulated Results                           | 68 |

| 4.2.5 Section Conclusion                                                 | 71  |

|--------------------------------------------------------------------------|-----|

| 4.3 Bulk-Driven DC Level Shifter                                         | 72  |

| 4.3.1 Introduction                                                       | 72  |

| 4.3.2 Proposal                                                           | 74  |

| 4.3.3 Simulated Results                                                  | 76  |

| 4.3.4 Section Conclusion                                                 | 79  |

| 4.4 Chapter Conclusion                                                   | 80  |

|                                                                          |     |

| Chapter 5 Bulk-Biased Cascodes                                           | 82  |

| 5.1 A 0.8-Volt Fully-Differential CMOS OTA Design                        |     |

| 5.1.1 Introduction                                                       |     |

| 5.1.2 Previous Essential Works                                           |     |

| 5.1.3 Proposal                                                           |     |

| 5.1.4 Simulation Results                                                 |     |

| 5.1.5 Section Conclusion                                                 |     |

| 5.2 Input Impedance of the Complementary BDDP                            |     |

| 5.3 Chapter Conclusion                                                   |     |

|                                                                          |     |

| Chapter 6 The BSIM3 Simulation and the Measurement of the Input          |     |

| Capacitance of a Bulk-Driven Buffer                                      |     |

| 6.1 Designing a Bulk-Driven CMOS Buffer for Fabrication                  |     |

| 6.2 Postlayout Simulation                                                |     |

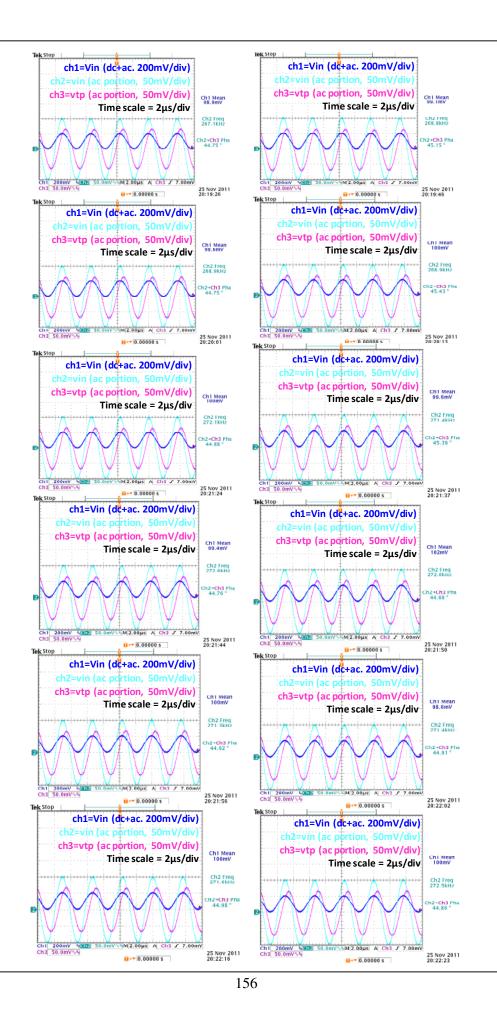

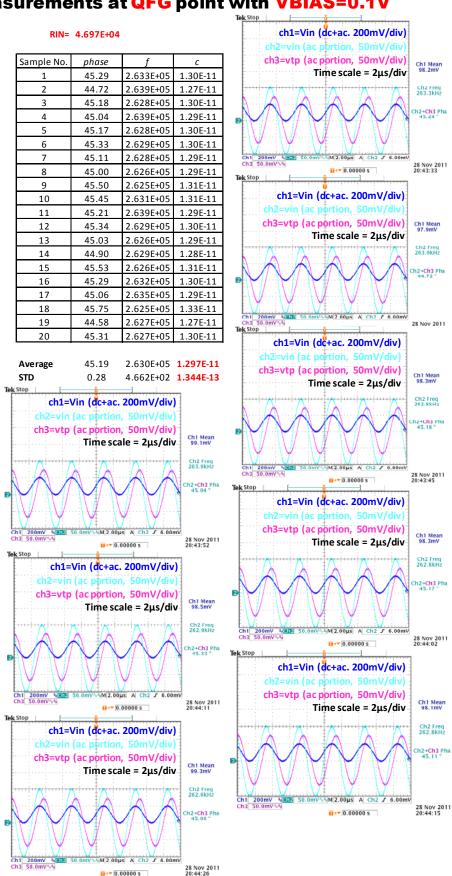

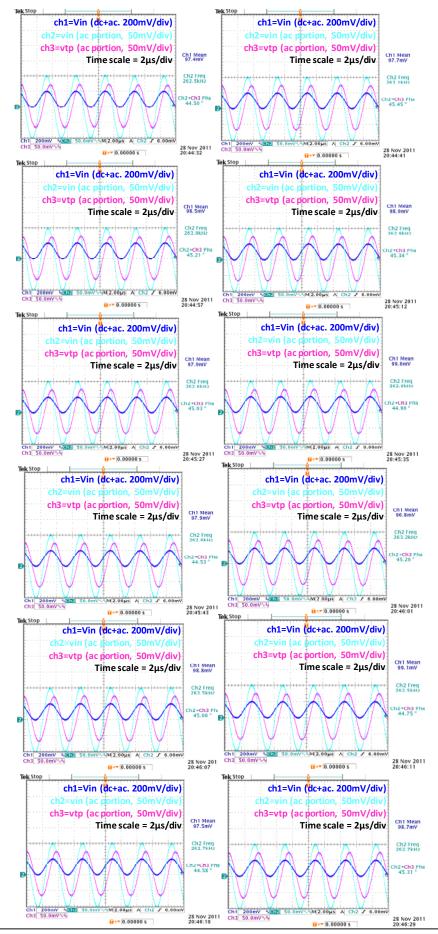

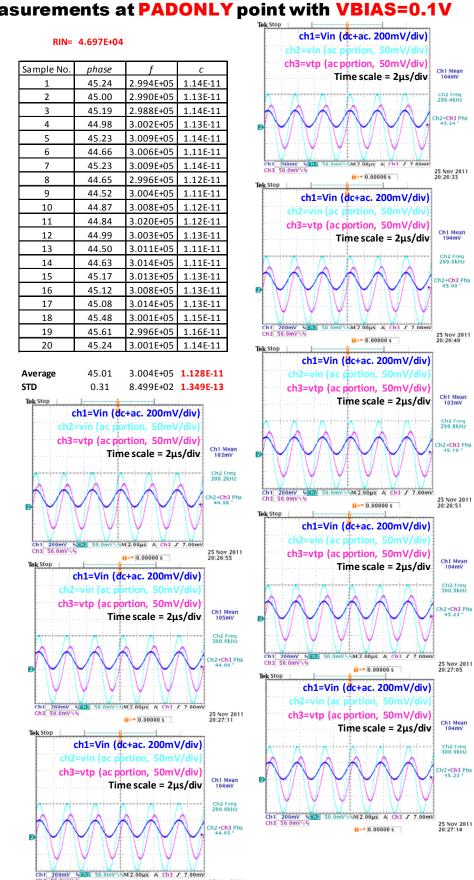

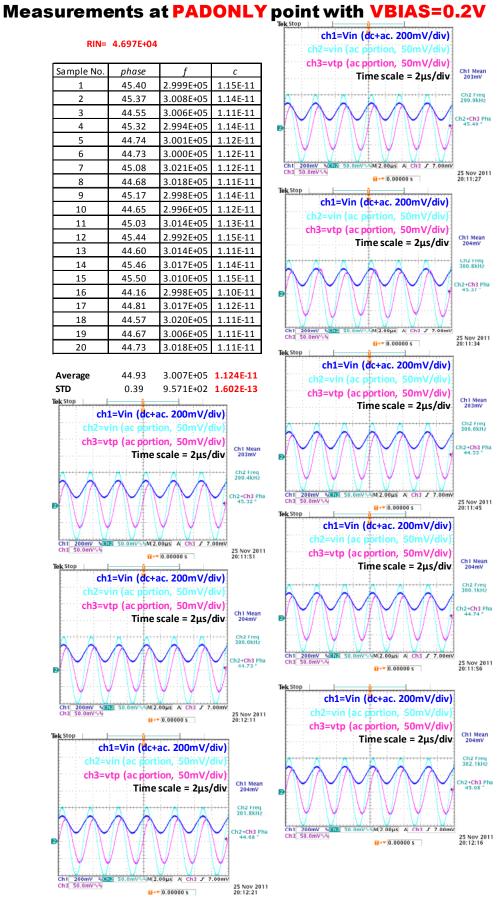

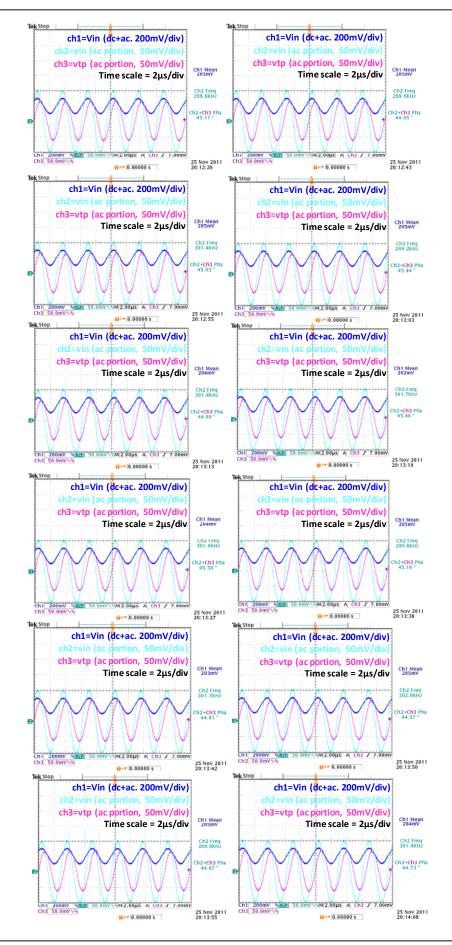

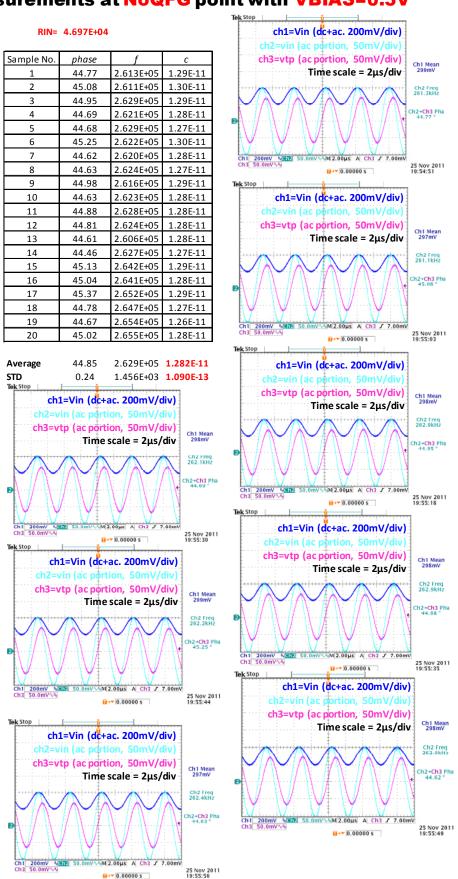

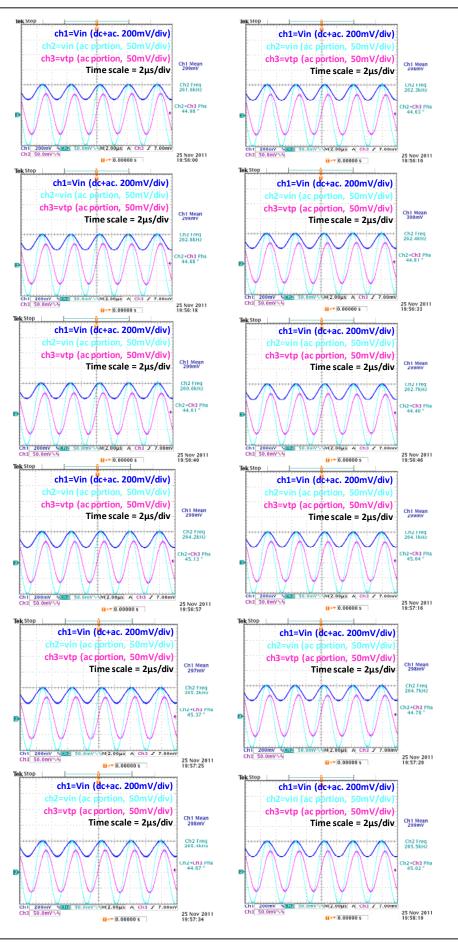

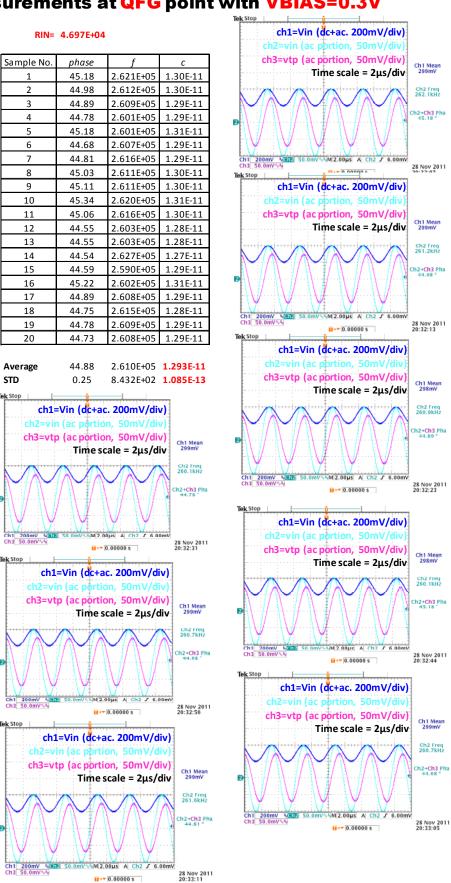

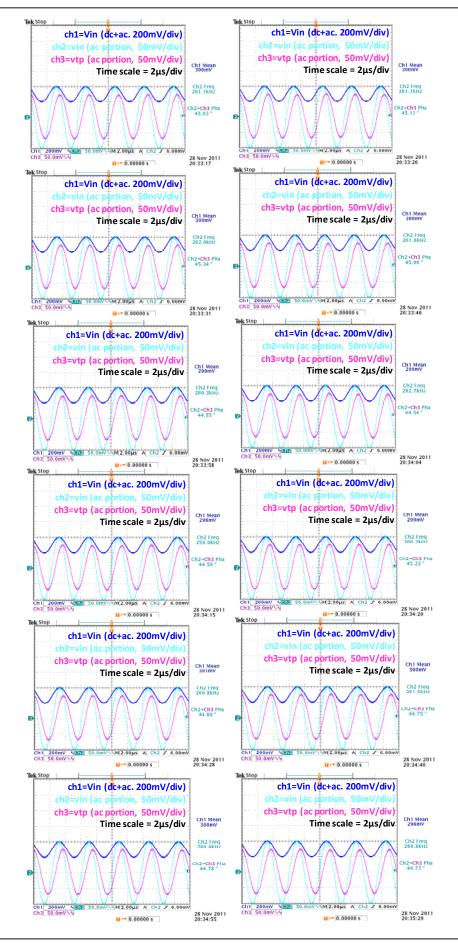

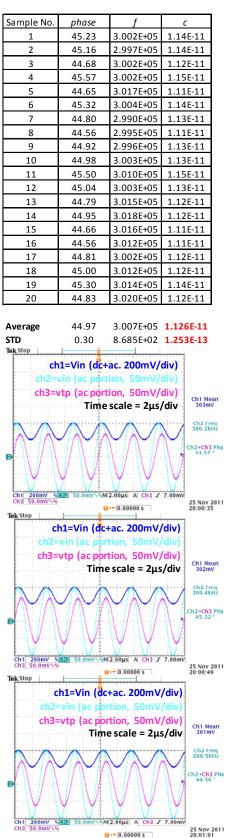

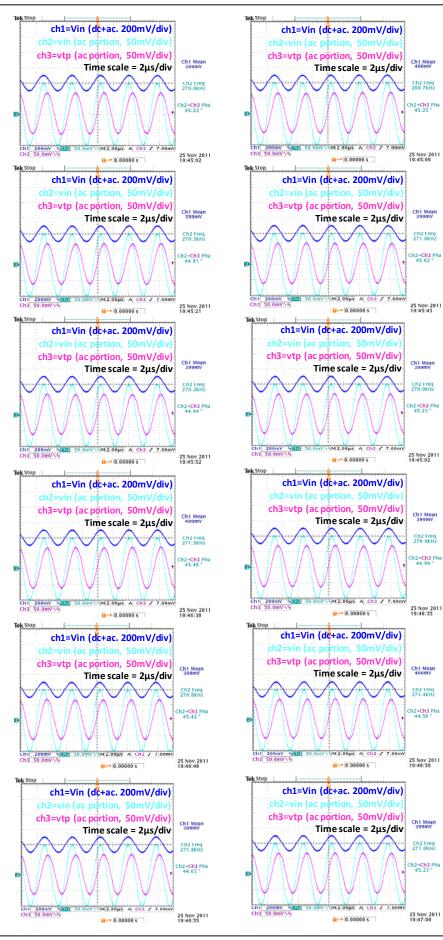

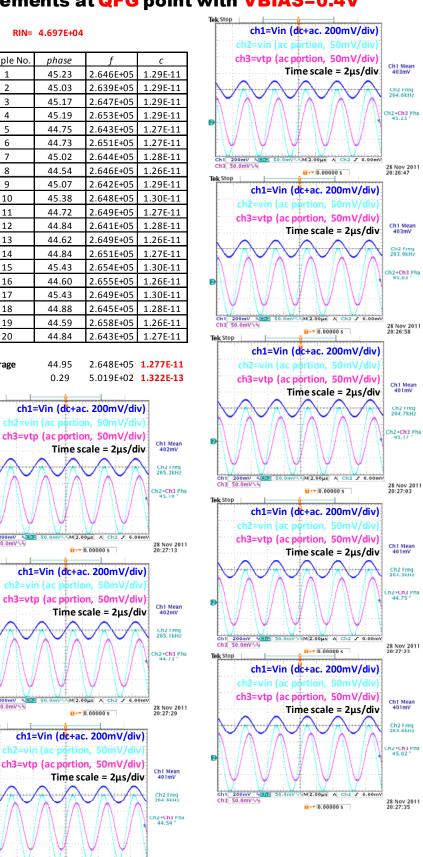

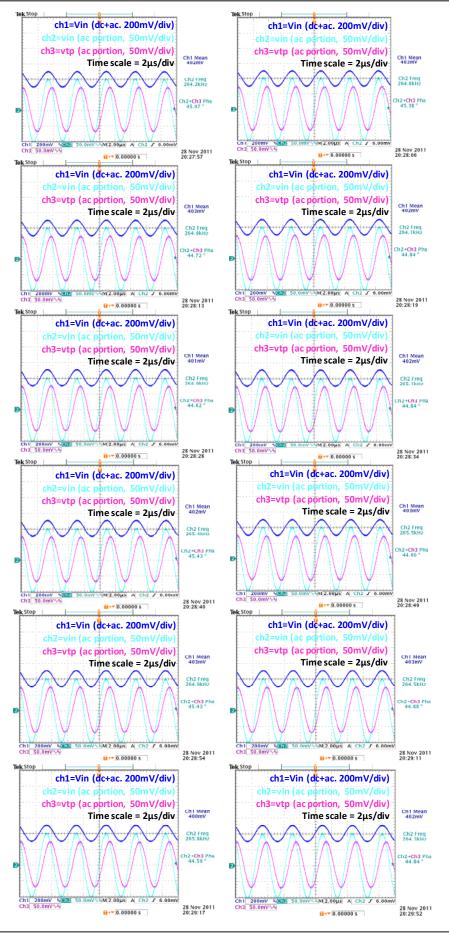

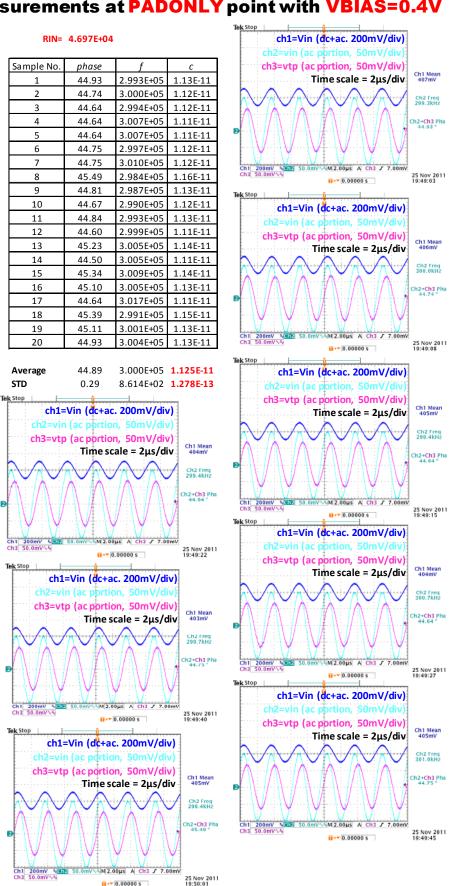

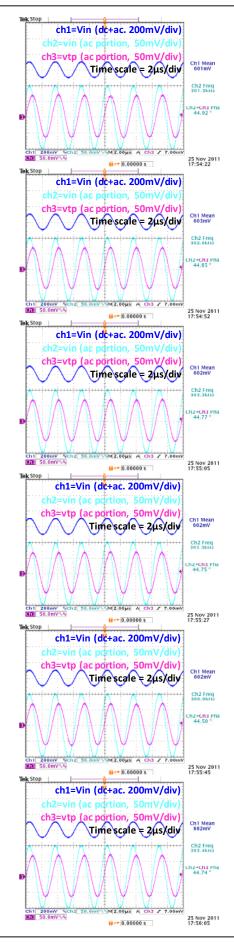

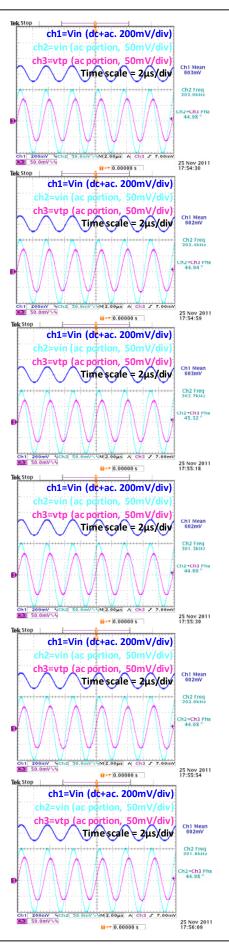

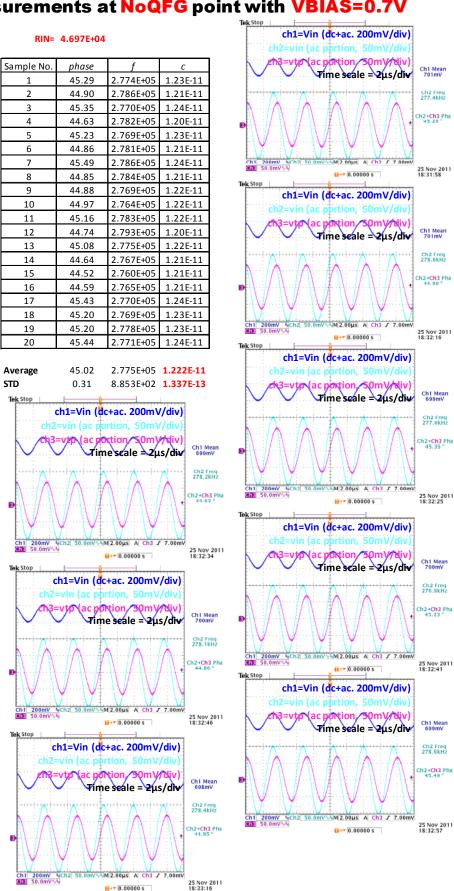

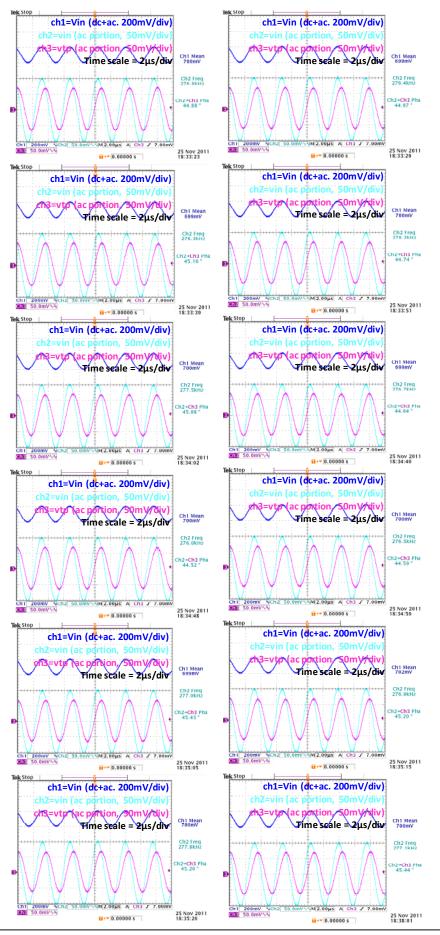

| 6.3 Measuring the Input Capacitance of the Fabricated Bulk-Driven Buffer | 107 |

| 6.4 Chapter Conclusion                                                   | 115 |

|                                                                          | 116 |

| Chapter 7 Conclusions                                                    |     |

| 7.1 Summary                                                              |     |

| 7.2 Recommendations for Further Work                                     | 118 |

| Appendix A Published Works                                               |     |

| Appendix B Supplementary Information to Chapter 6                        |     |

| B.1 SPICE Code for Simulating the Input Capacitance                      | 148 |

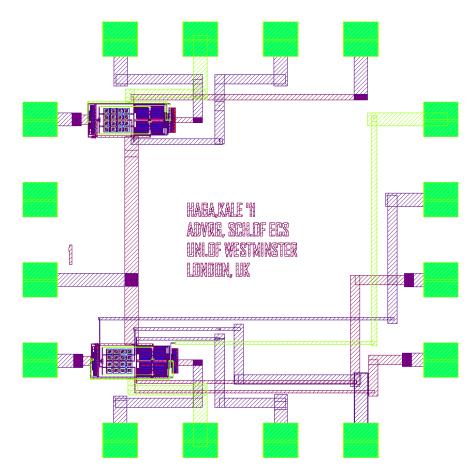

| B.2 IC Layout of the Whole Die                                           |     |

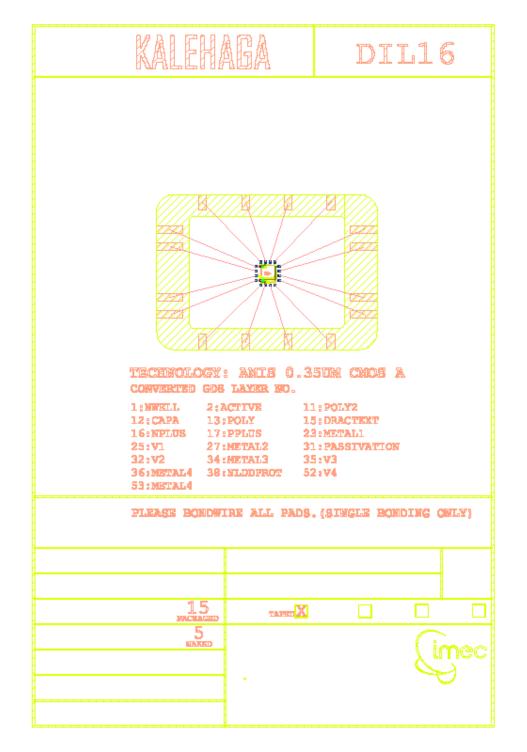

| B.3 Bonding Diagram                                                | 151 |

|--------------------------------------------------------------------|-----|

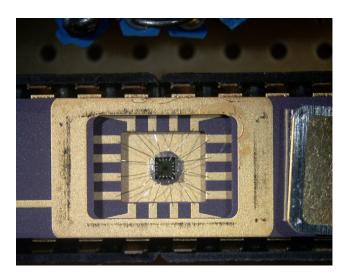

| B.4 More Snapshots of the Microphotograph of the Fabricated Device |     |

| B.5 Test Board                                                     |     |

| Appendix C Logs of Measurement Data                                | 154 |

| References                                                         | 221 |

## List of Figures

| Figure 1-1 CMOS Technology Roadmap [ITR10]2                                                                                                                                                                |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 1-2 Supply Voltage Reduction Roadmap [ITR10]                                                                                                                                                        |

| Figure 1-3 (a) Op-amp in unity-gain configuration, (b) complementary differential pair, and (c) illustration describing dead-band region under low-supply voltage condition5                               |

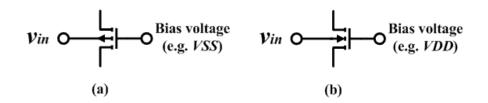

| Figure 1-4 (a) pMOS bulk-driven device, and (b) nMOS bulk-driven device6                                                                                                                                   |

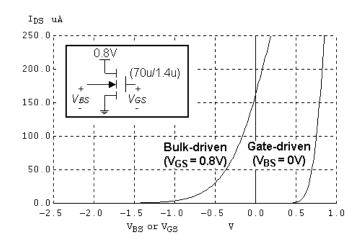

| Figure 2-1 Simulating transconductance characteristics of gate-driven and bulk-driven nMOS transistors using a 0.35µm CMOS technology16                                                                    |

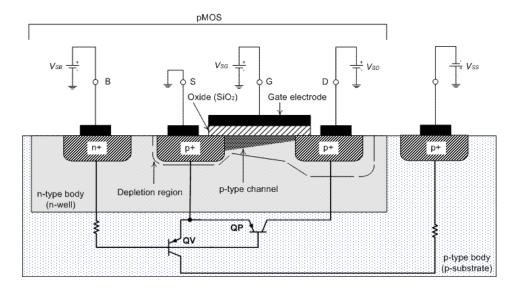

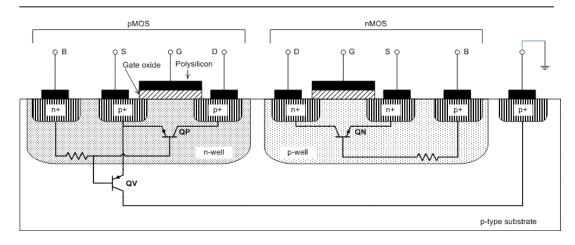

| Figure 2-2 Cross sectional view of a bulk-driven pMOS device in an n-well CMOS technology                                                                                                                  |

| Figure 2-3 Cross sectional view of twin-well CMOS technology20                                                                                                                                             |

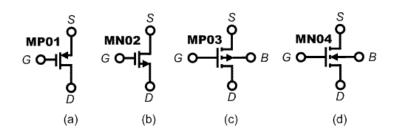

| Figure 3-1 MOSFET symbols for (a) pMOS (its bulk tied to VDD and not shown), (b) nMOS (its bulk tied to VSS and not shown), (c) pMOS (its bulk shown explicitly), and (d) nMOS (its bulk shown explicitly) |

| Figure 3-2 The bulk-driven RBS proposed in [BLA00]                                                                                                                                                         |

| Figure 3-3 Topology of the BDDRB input stage                                                                                                                                                               |

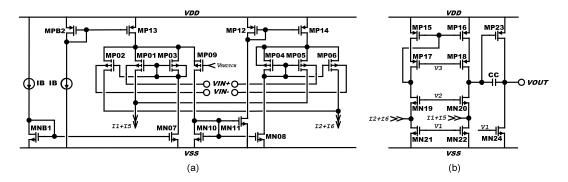

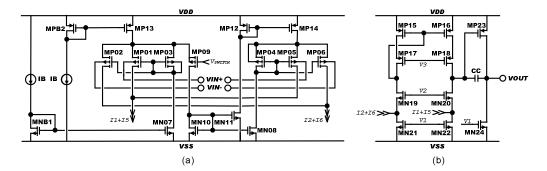

| Figure 3-4 An application example of the BDDRB input stage in a folded-cascode two-<br>stage op-amps (a) the BDDRB input stage, and (b) a folded-cascode two-stage op-amps<br>                             |

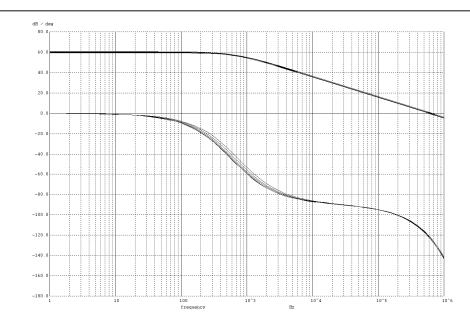

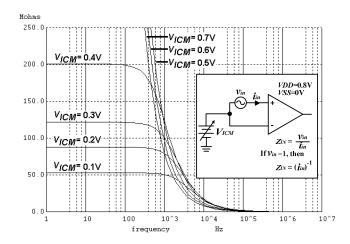

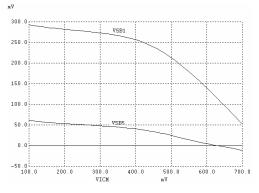

| Figure 3-5 Simulated frequency response of the op-amps for $V_{ICM}$ varying from 0.1 to 0.7V with a 0.1V step                                                                                             |

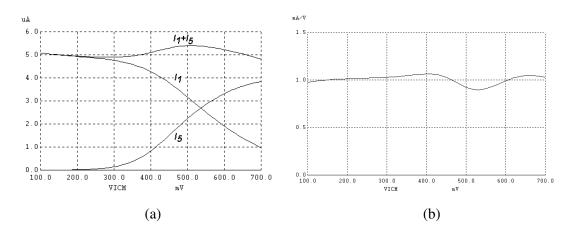

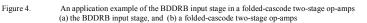

| Figure 3-6 Simulated plots for (a) tail current versus $V_{ICM}$ and (b) $g_m(eff)$ versus $V_{ICM}$ 36                                                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

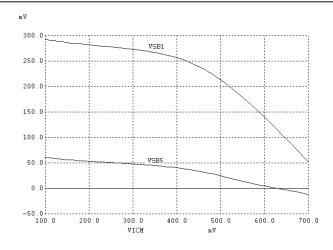

| Figure 3-7 Simulated $V_{SB1}$ and $V_{SB5}$ versus $V_{ICM}$                                                                                                |

| Figure 3-8 Simulation results of the circuit-level input impedance characteristic                                                                            |

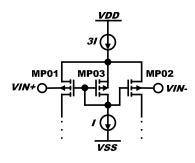

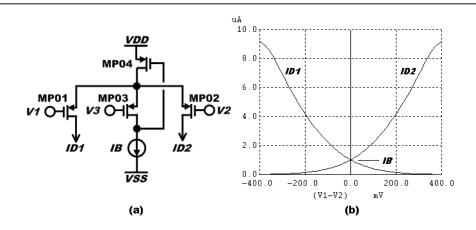

| Figure 3-9 (a) (pMOS) FVFDP proposed in [CAR05], and (b) simulating the DC transfer characteristics using a 0.35µm CMOS process                              |

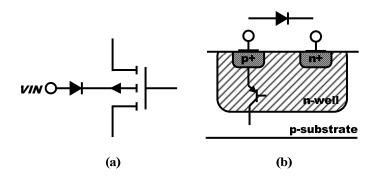

| Figure 3-10 (a) a bulk-driven pMOS device with the reversed-biased diode, and (b) a diode realised in CMOS technology                                        |

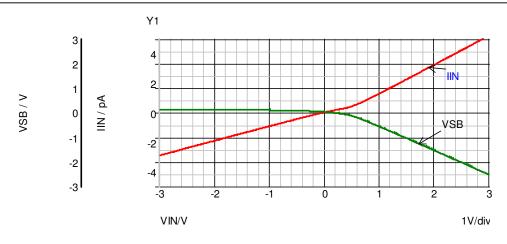

| Figure 3-11 Simulated $I_{IN}$ and $V_{SB}$ of Figure 2(a)                                                                                                   |

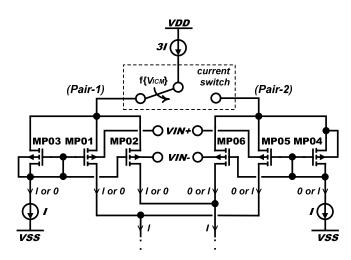

| Figure 3-12 Proposed CMOS buffer using Bulk-Driven Flipped Voltage Differential<br>Pair                                                                      |

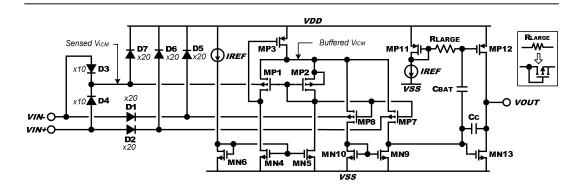

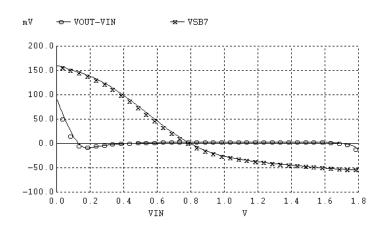

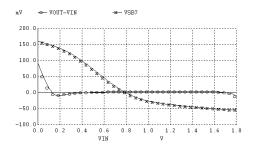

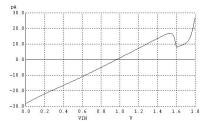

| Figure 3-13 Simulated $V_{OUT}$ - $V_{IN}$ and $V_{SB7}$ of Figure 3-12 in unity-gain configuration45                                                        |

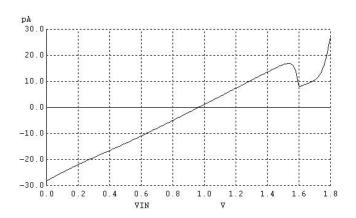

| Figure 3-14 Simulated <i>I</i> <sub>IN</sub> of Figure 3-12 in unity-gain configuration                                                                      |

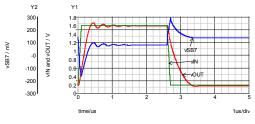

| Figure 3-15 Simulated $v_{SB7}$ and slew rate of $v_{out}$ of Figure 3-12 in unity-gain configuration with CL=5pF ( $v_{IN}$ stepping between 0.2V and 1.6V) |

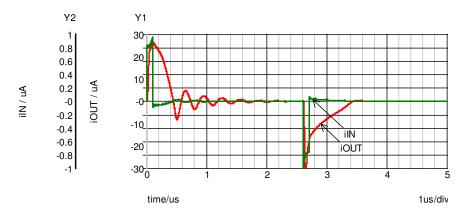

| Figure 3-16 Simulated $i_{IN}$ and $i_{OUT}$ of Figure 4 in unity-gain configuration with CL=5pF ( $v_{IN}$ stepping between 0.2V and 1.6V)                  |

| Figure 3-17 Gate-driven Flipped Voltage Differential Pair                                                                                                    |

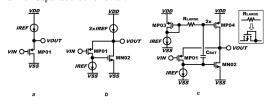

| Figure 4-1 Voltage followers (a) common-drain amplifier (voltage follower) and (b)<br>FVF proposed in [CAR05]                                                |

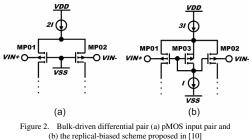

| Figure 4-2 Bulk-driven differential pair (a) pMOS input pair and (b) the replica-biased scheme proposed in [BLA00]                                           |

| Figure 4-3 Bulk-driven flipped voltage follower (class-A)                                                                                                    |

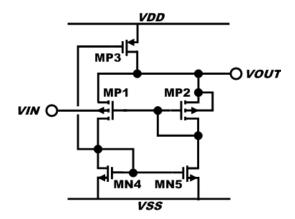

| Figure 4-4 Proposed class-AB bulk-driven flipped voltage follower                                                                                              |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

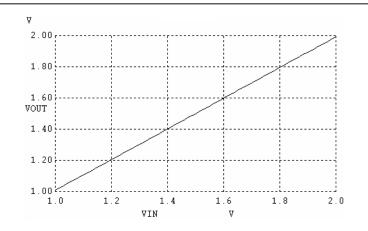

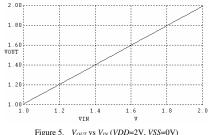

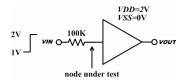

| Figure 4-5 $V_{OUT}$ vs $V_{IN}$ (VDD=2V, VSS=0V)                                                                                                              |

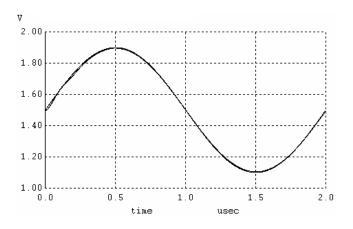

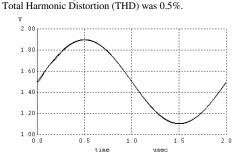

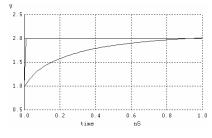

| Figure 4-6 <i>V<sub>OUT</sub></i> and <i>V<sub>IN</sub></i> with 0.8Vpp 500kHz sinusoidal input ( <i>VDD</i> =2V, <i>VSS</i> =0V, CL=10pF)                     |

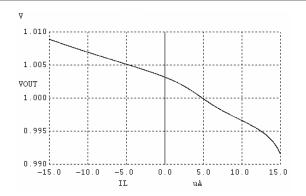

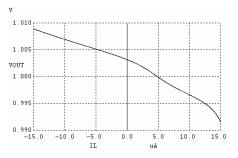

| Figure 4-7 Load regulation ( $VDD=2V$ , $VSS=0V$ , $V_{IN}=1V$ )                                                                                               |

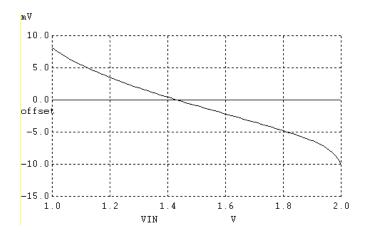

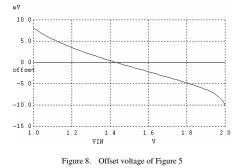

| Figure 4-8 Offset voltage                                                                                                                                      |

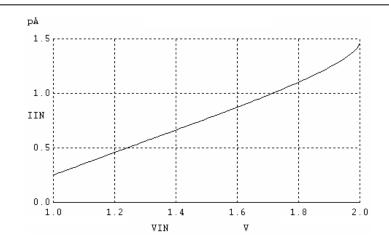

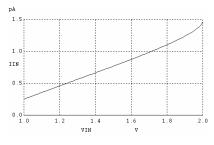

| Figure 4-9 Input current ( <i>VDD</i> =2V, <i>VSS</i> =0V)61                                                                                                   |

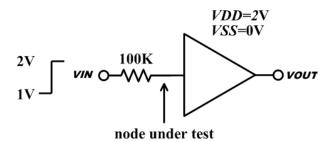

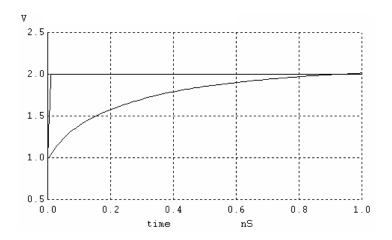

| Figure 4-10 Simulation setup for the input capacitance                                                                                                         |

| Figure 4-11 Simulation results for the Figure 10 setup                                                                                                         |

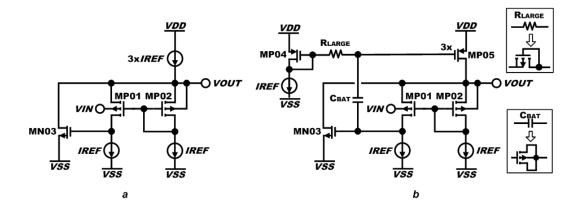

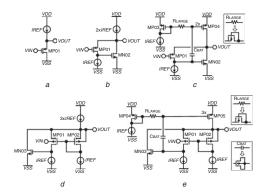

| Figure 4-12 (a) class-A source follower, (b) class-A SSF, and (c) class-AB SSF proposed by Lopez-Martin <i>et al</i> [LOP09]                                   |

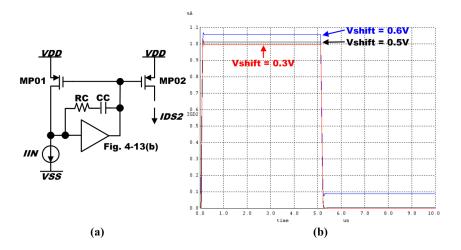

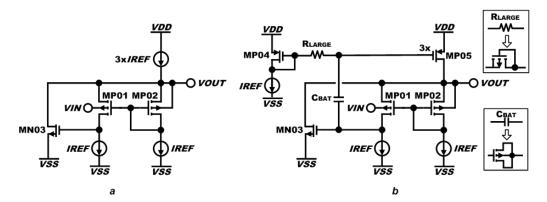

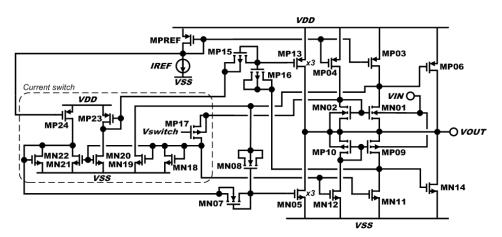

| Figure 4-13 BDSSF (a) class-A operation, and (b) converting into class-AB operation                                                                            |

| using the QFG technique proposed by Ramìrez-Angulo et al [LOP09] [RAM04]66                                                                                     |

| Figure 4-14 Class-AB rail-to-rail CMOS analogue buffer using a complementary pair of BDSSF                                                                     |

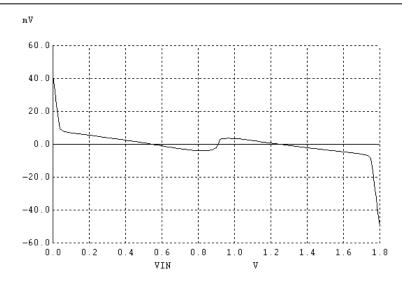

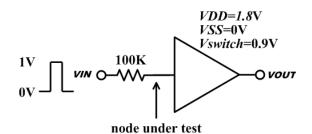

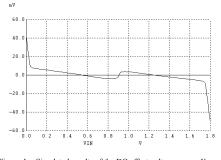

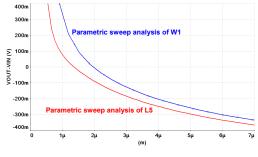

| Figure 4-15 Simulated results of the DC offset voltage versus $V_{IN}$ ( <i>VDD</i> =1.8V, <i>VSS</i> =0V, <i>Vswitch</i> =0.9V)                               |

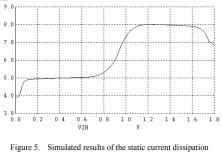

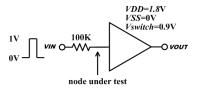

| Figure 4-16 Simulated results of the static current dissipation ( <i>VDD</i> =1.8V, <i>VSS</i> =0V, <i>Vswitch</i> =0.9V)                                      |

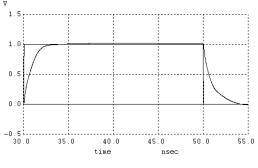

| Figure 4-17 $V_{OUT}$ vs $V_{IN}$ and $I_{OUT}$ with $V_{IN} = 1.6$ Vpp 100kHz sinewave and CL =68pF ( <i>VDD</i> =1.8V, <i>VSS</i> =0V, <i>Vswitch</i> =0.9V) |

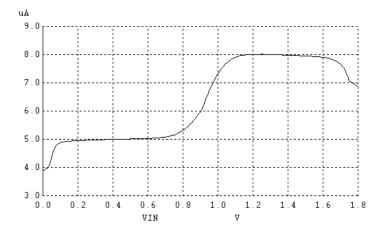

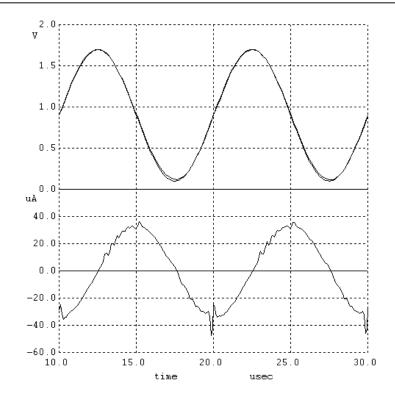

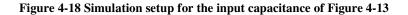

| Figure 4-18 Simulation setup for the input capacitance of Figure 4-1370                                                                                        |

| Figure 4-19 Simulation results for the Figure 4-18 setup71                                                                                                     |

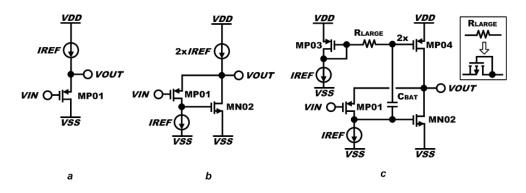

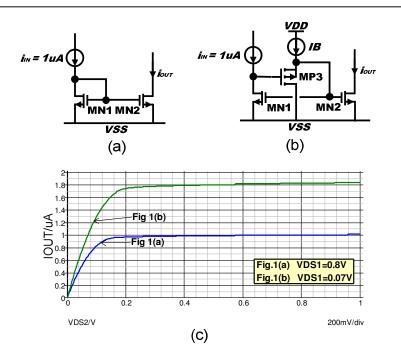

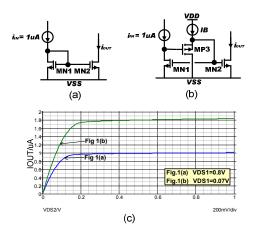

| Figure 4-20(a) Simple current mirror with $I_{IN}=1\mu A$ , (b) with a DC level shifter, and (c) |

|--------------------------------------------------------------------------------------------------|

| the $V_{DS2}$ DC-sweep simulated results                                                         |

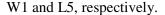

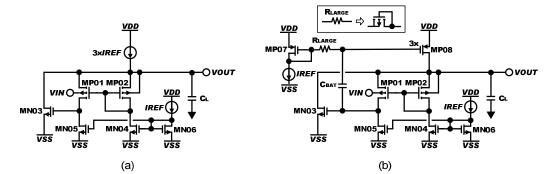

| Figure 4-21 Parametric sweep simulation of Figure 4-13(a) and (b)75                              |

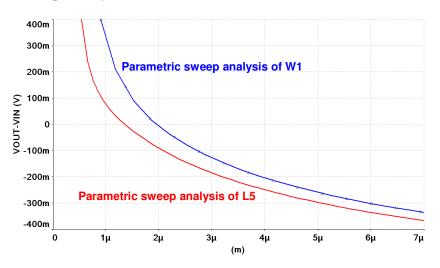

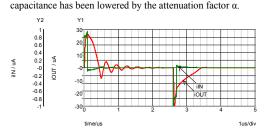

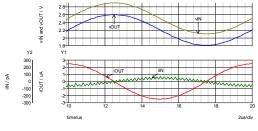

| Figure 4-22 Simulated results of Fig. 2(b) with W1=3W2 and $I_{DS1}=I_{DS2}$ , where $v_{IN}=$   |

| 0.8Vpp, 100kHz sinusoidal wave and CL with 10pF77                                                |

| Figure 4-23 (a) A pMOS current mirror with level shifted BDSSF and (b) simulated plot            |

| of 1µA step response                                                                             |

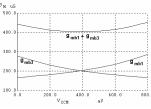

| Figure 5-1 Simulating transconductance characteristics of gate-driven and bulk-driven            |

| nMOS transistors using a 0.35µm CMOS technology                                                  |

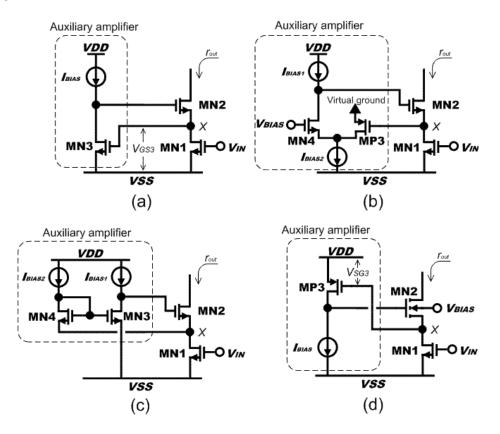

| Figure 5-2 Gain-boosting topology with different auxiliary amplifiers, (a) common-               |

| source stage [HOS79] (b) folded-cascode [RAZ01], (c) common-source stage with a                  |

| level shifter [COB94], and (d) complementary common-source stage [ROS04]86                       |

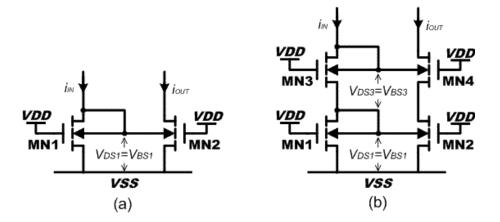

| Figure 5-3 Bulk-driven current mirror (a) simple [BLA95] and (b) cascode [BLA96]88               |

|                                                                                                  |

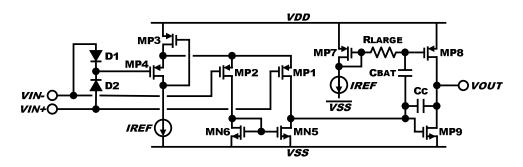

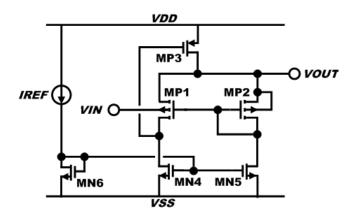

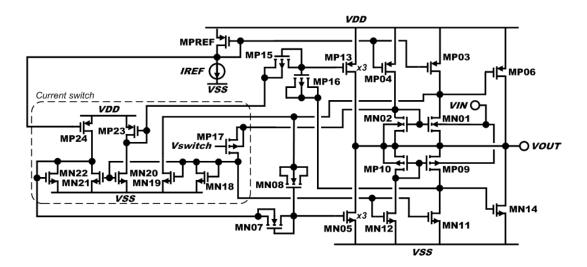

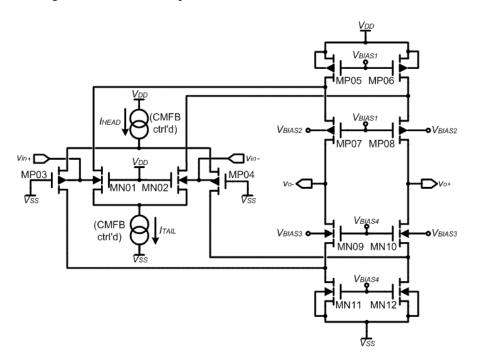

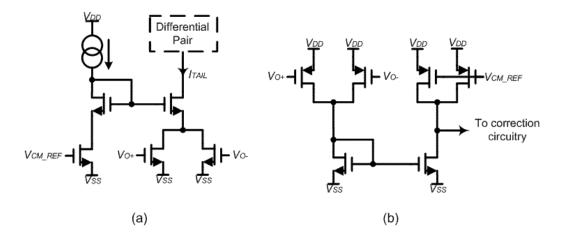

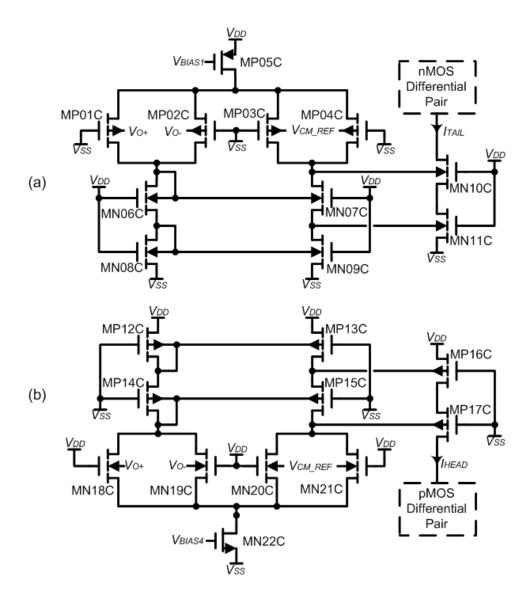

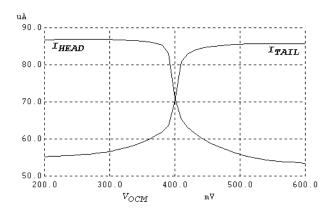

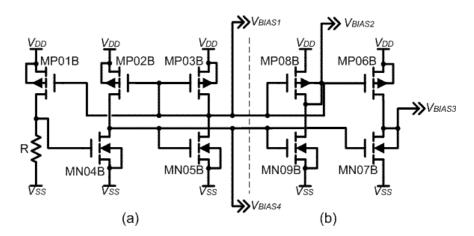

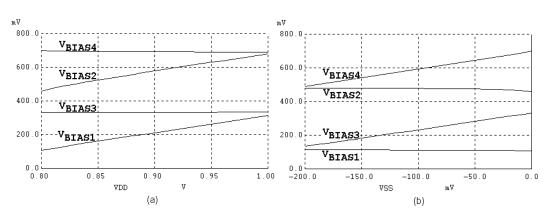

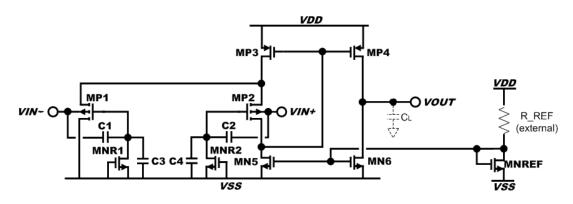

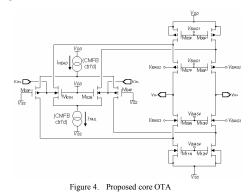

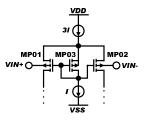

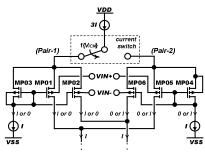

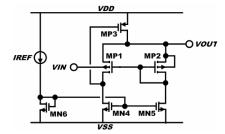

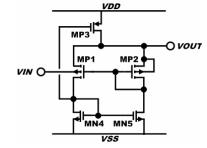

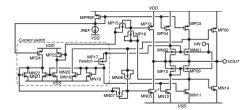

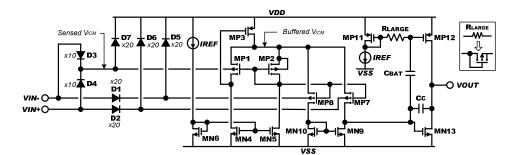

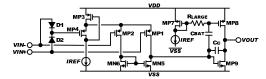

| Figure 5-4 Proposed core OTA                                                                     |

| Figure 5-4 Proposed core OTA                                                                     |

|                                                                                                  |

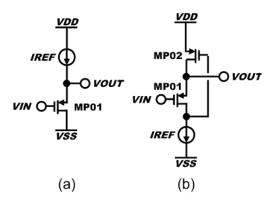

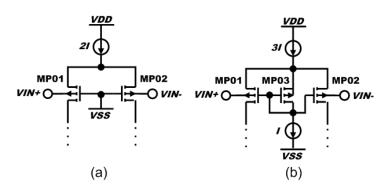

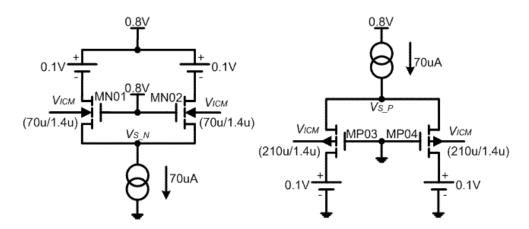

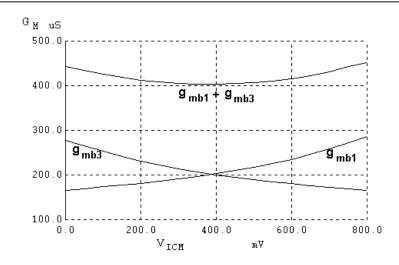

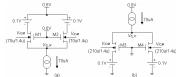

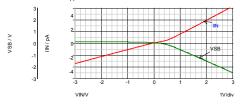

| Figure 5-5 Setup for simulating (a) $g_{mb1}$ and (b) $g_{mb3}$                                  |

| Figure 5-5 Setup for simulating (a) $g_{mb1}$ and (b) $g_{mb3}$                                  |

| Figure 5-5 Setup for simulating (a) $g_{mb1}$ and (b) $g_{mb3}$                                  |

| Figure 5-5 Setup for simulating (a) $g_{mb1}$ and (b) $g_{mb3}$                                  |

| Figure 5-5 Setup for simulating (a) $g_{mb1}$ and (b) $g_{mb3}$                                  |

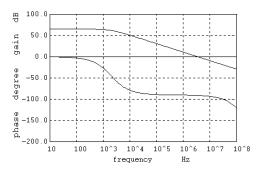

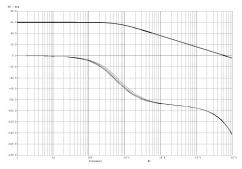

| Figure 5-12 Simulated plots of open-loop gain and phase margin                                                                                                                                                                                                                                                                                     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

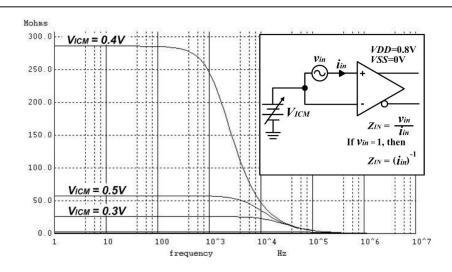

| Figure 5-13 Simulation results of the circuit-level input impedance characteristics of the                                                                                                                                                                                                                                                         |

| proposed OTA utilising the complementary BDDP stage                                                                                                                                                                                                                                                                                                |

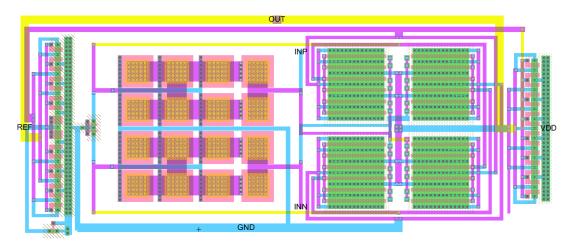

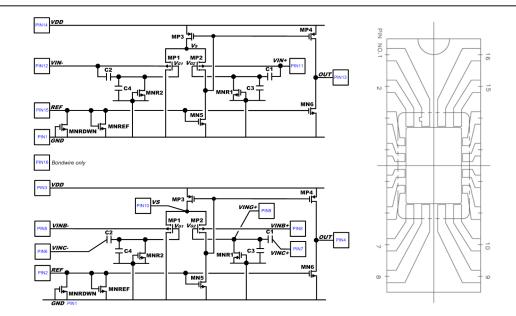

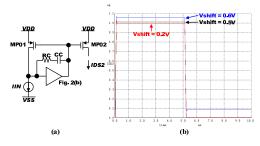

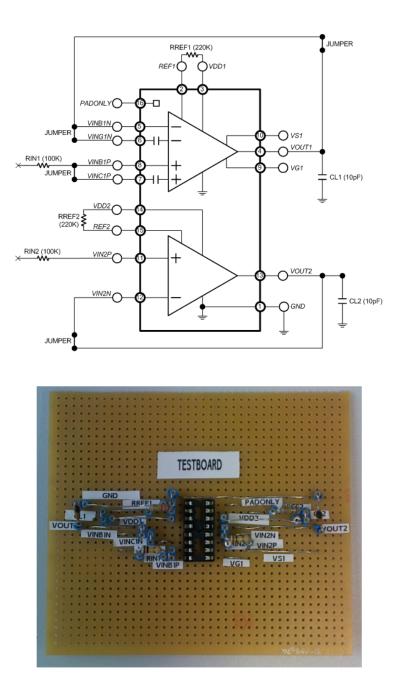

| Figure 6-1 Circuit Diagram of the Bulk-Driven CMOS Buffer for Fabrication101                                                                                                                                                                                                                                                                       |

| Figure 6-2 Layout Design of the Bulk-Driven CMOS Buffer of Figure 6-1102                                                                                                                                                                                                                                                                           |

| Figure 6-3 Pin Assignment                                                                                                                                                                                                                                                                                                                          |

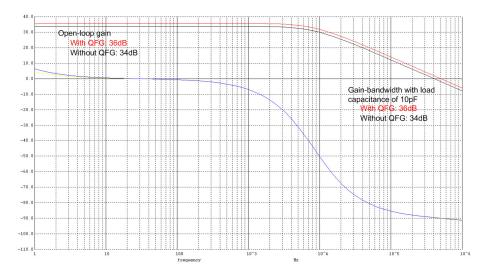

| Figure 6-4 Postlayout Simulation Results of the Frequency Response (VDD=1V,                                                                                                                                                                                                                                                                        |

| VSS=0V, CL=10pF)                                                                                                                                                                                                                                                                                                                                   |

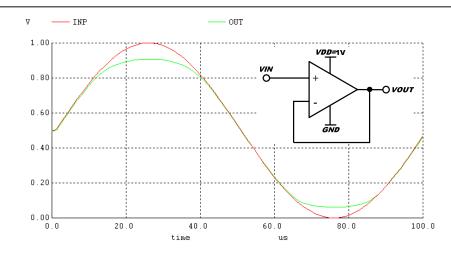

| Figure 6-5 Postlayout Simulation Result of the Output Waveform with a 1Vp-p 10kHz                                                                                                                                                                                                                                                                  |

| Sinusoidal Input                                                                                                                                                                                                                                                                                                                                   |

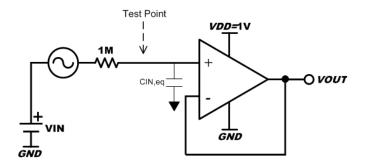

| Figure 6-6 The Setup for Simulating $C_{IN,eq}$                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                    |

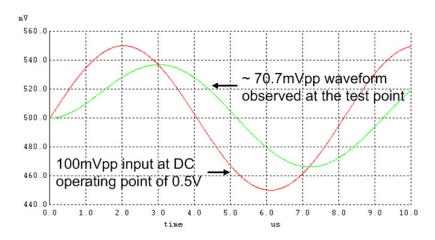

| Figure 6-7 Postlayout Simulation of Figure 6-6 with the Input DC Operating Point at                                                                                                                                                                                                                                                                |

| Figure 6-7 Postlayout Simulation of Figure 6-6 with the Input DC Operating Point at 0.5V                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                    |

| 0.5V                                                                                                                                                                                                                                                                                                                                               |

| 0.5V                                                                                                                                                                                                                                                                                                                                               |

| 0.5V                                                                                                                                                                                                                                                                                                                                               |

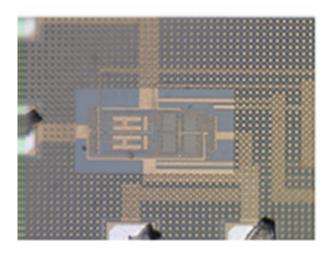

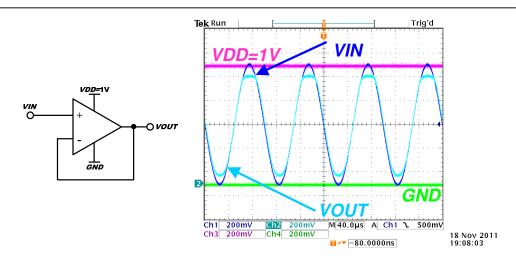

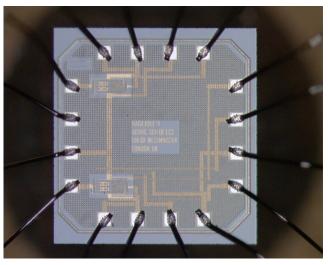

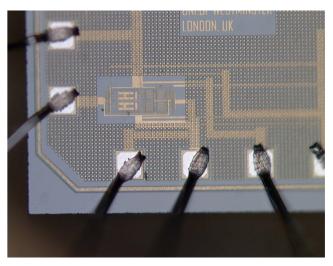

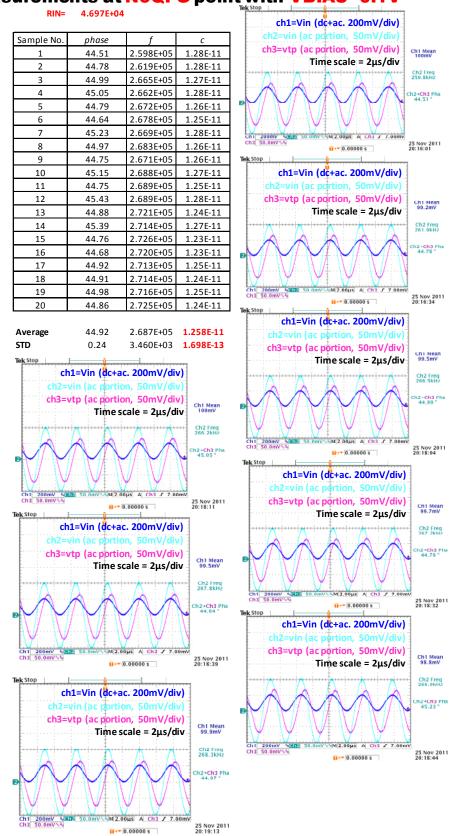

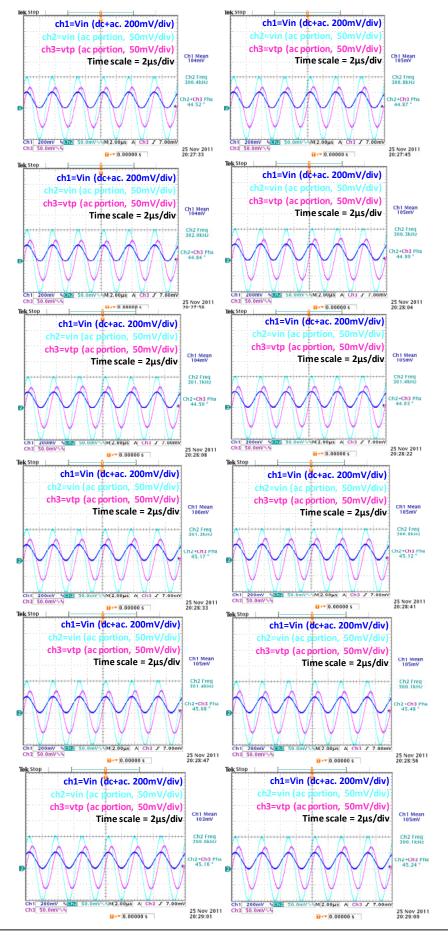

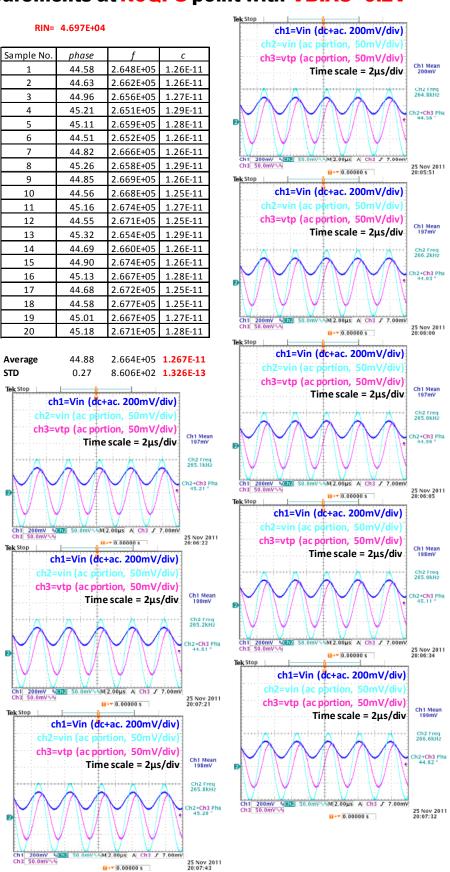

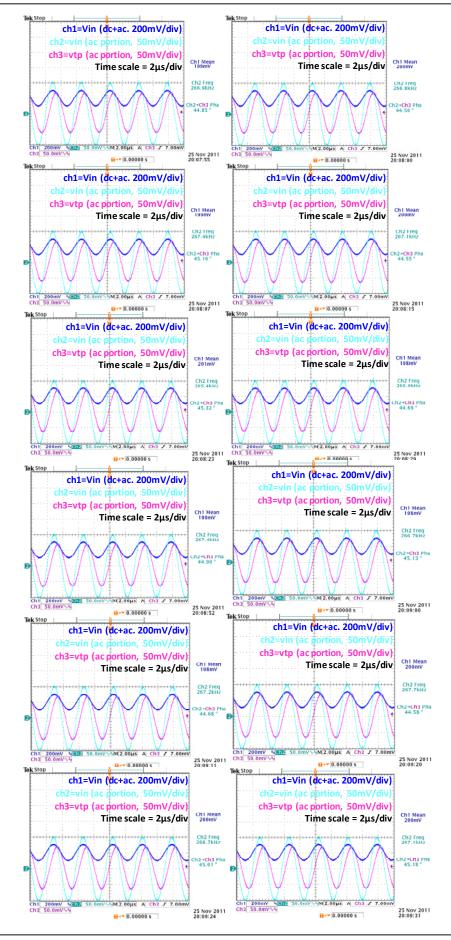

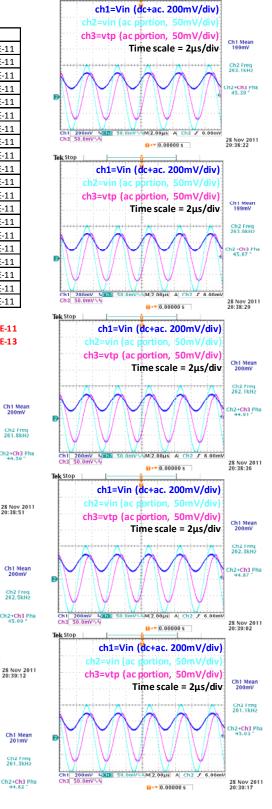

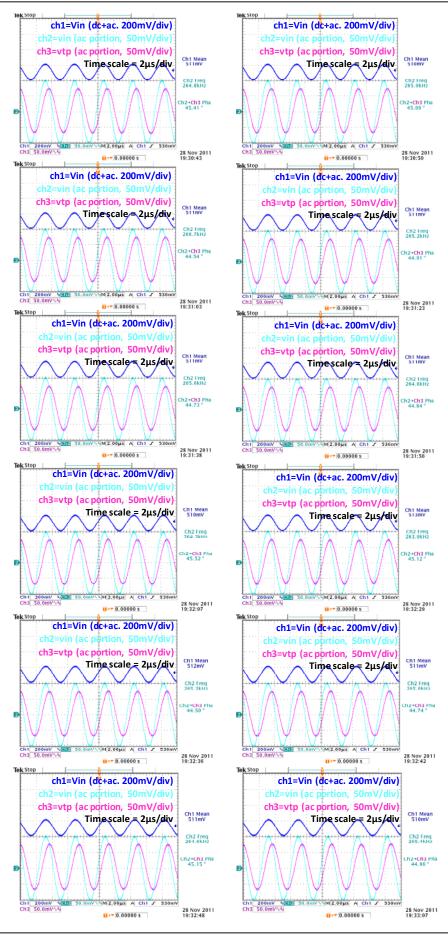

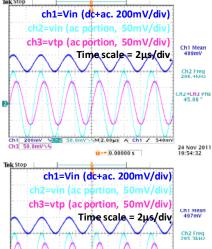

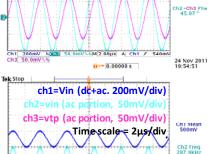

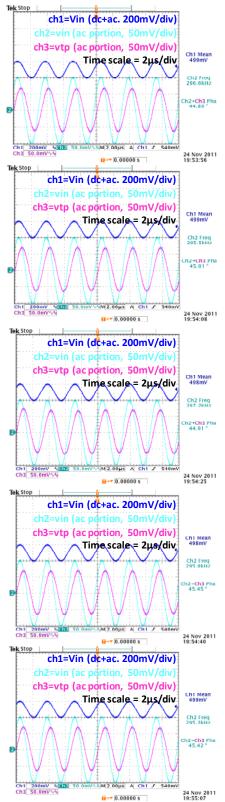

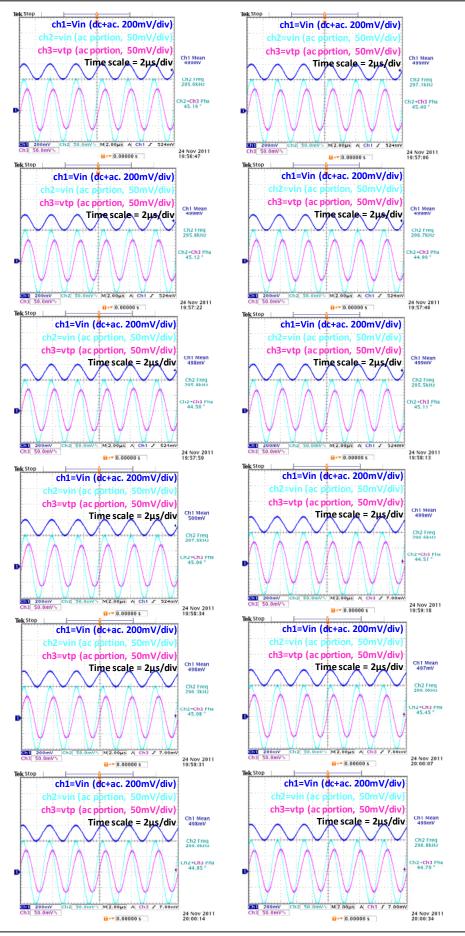

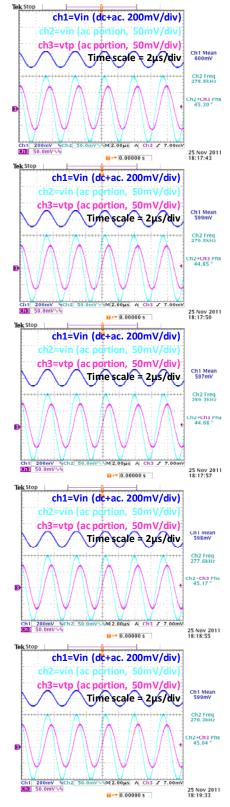

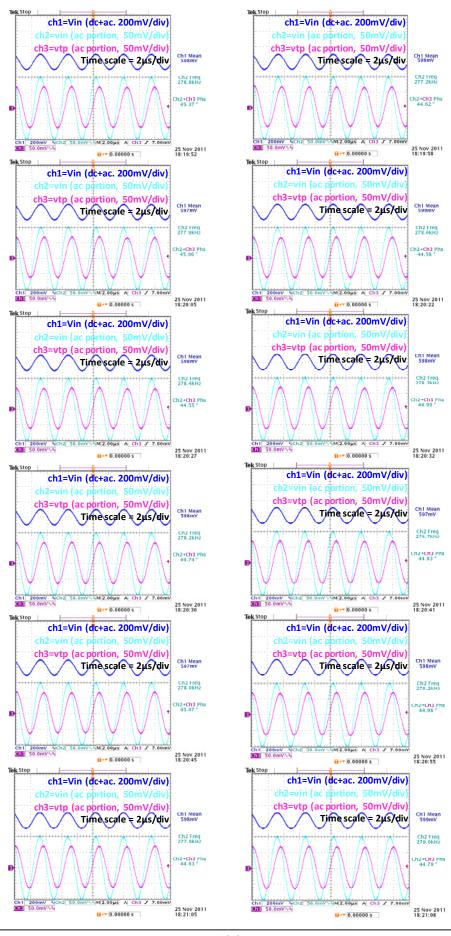

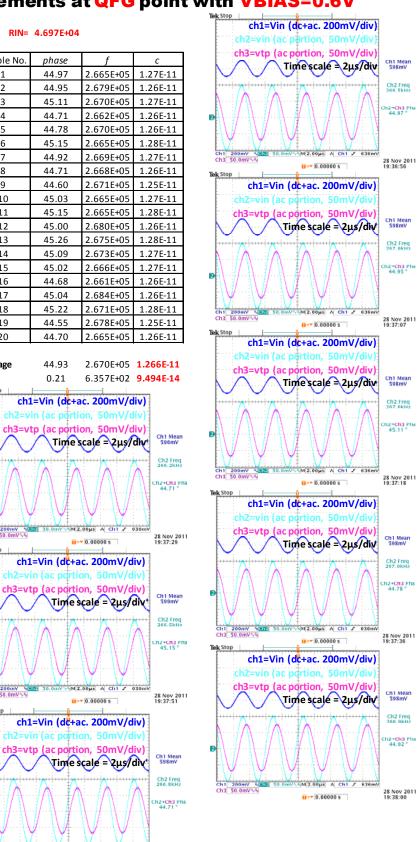

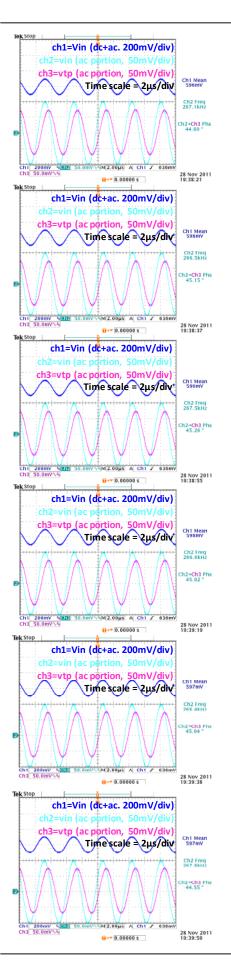

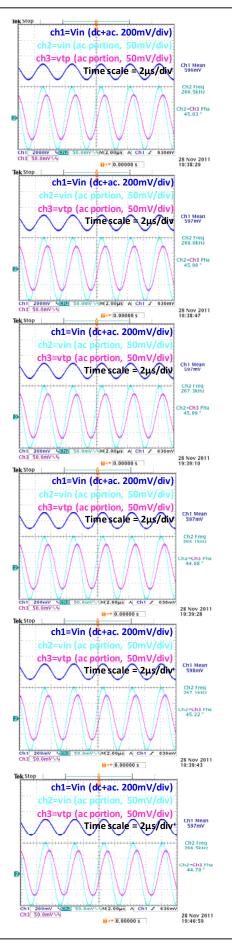

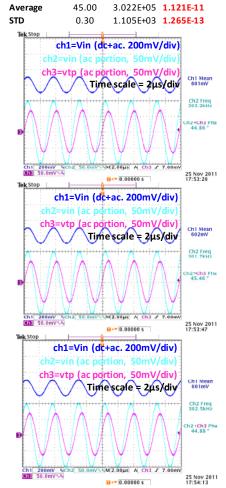

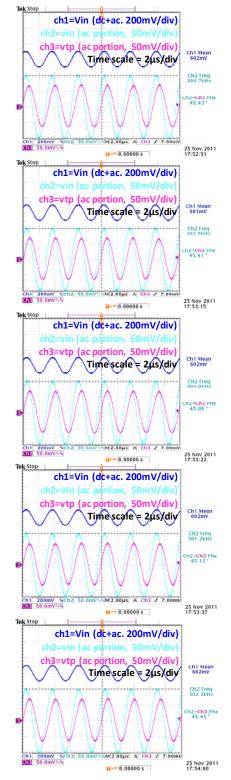

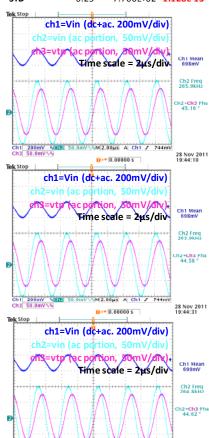

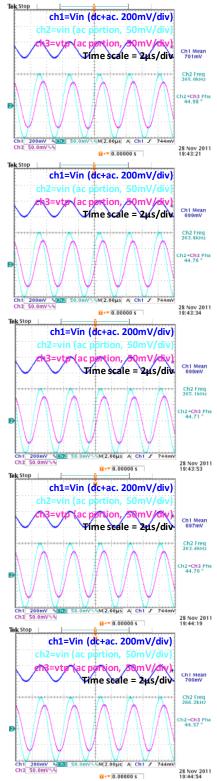

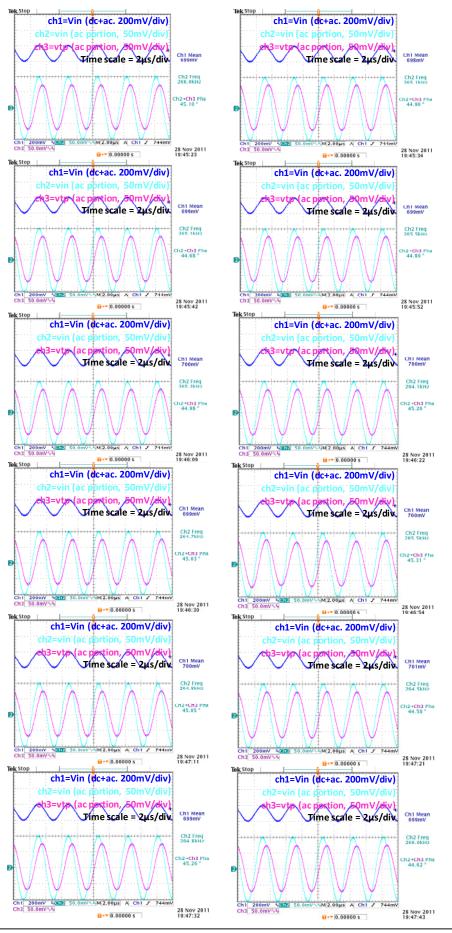

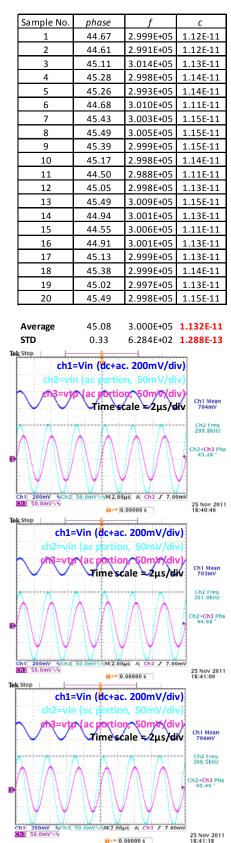

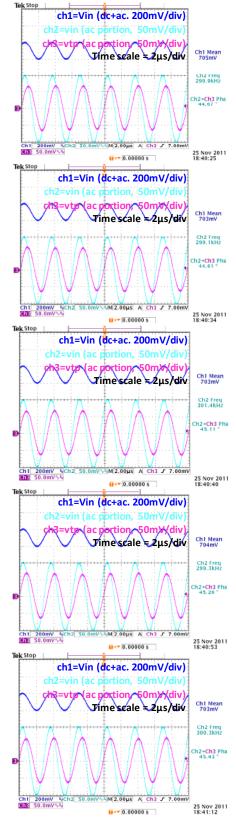

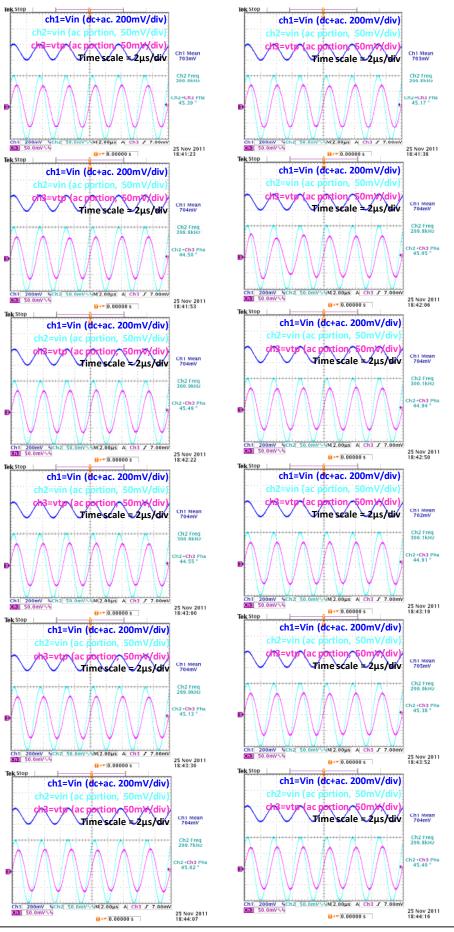

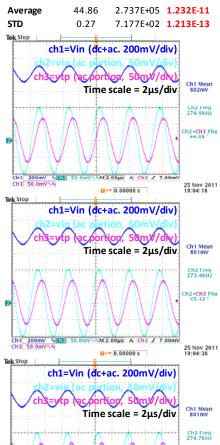

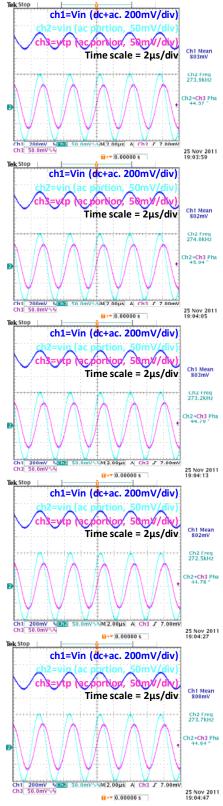

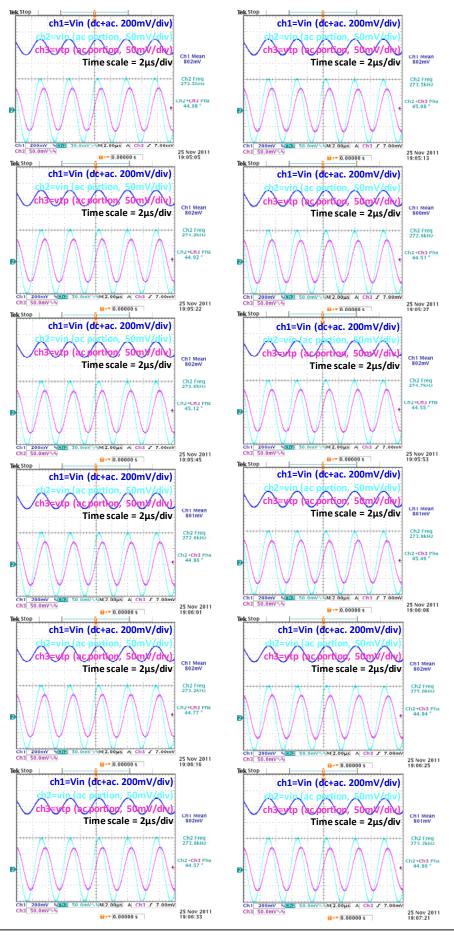

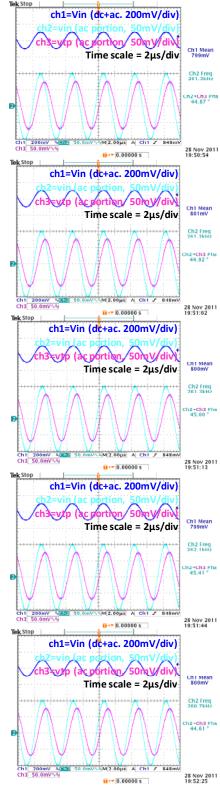

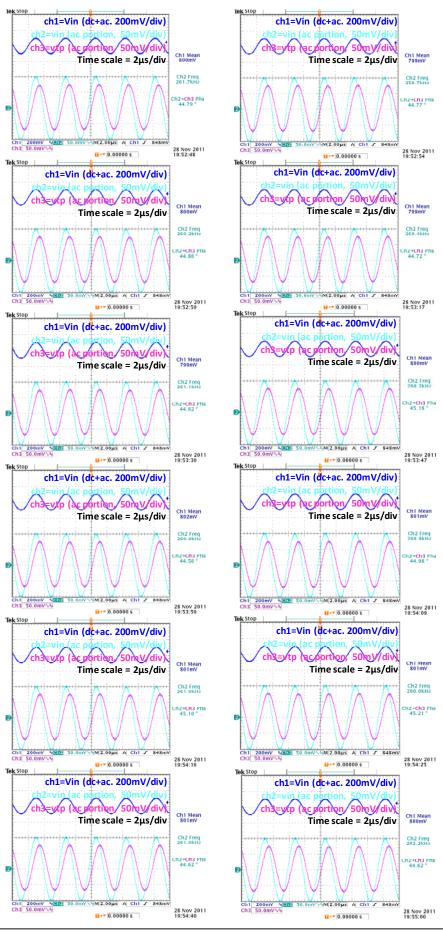

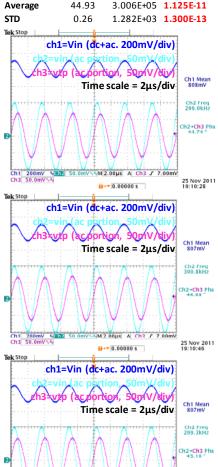

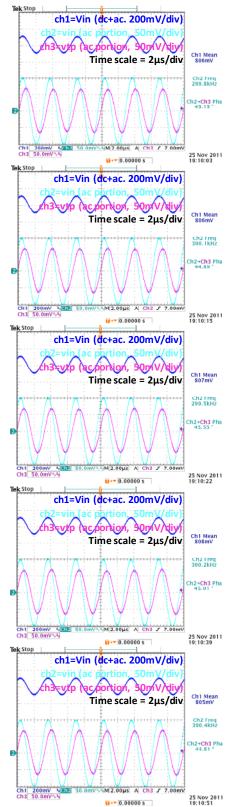

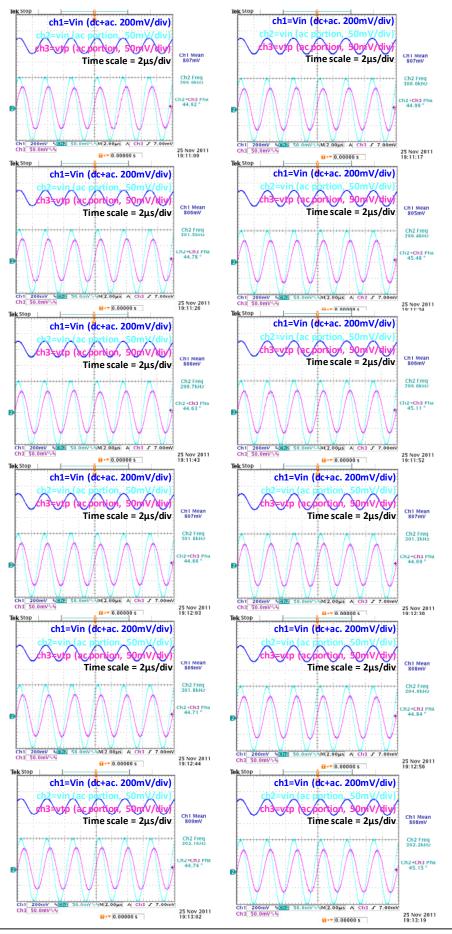

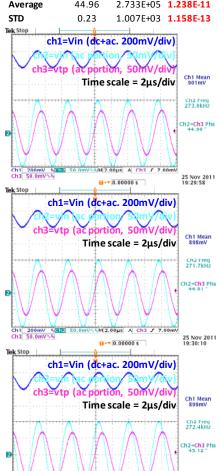

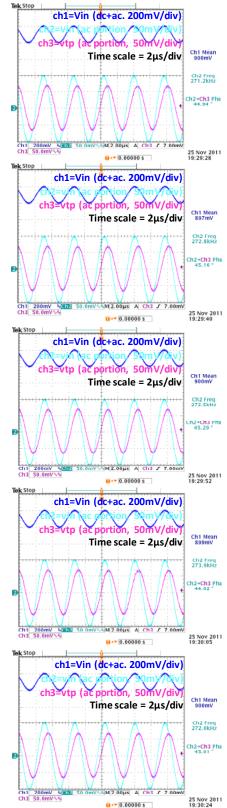

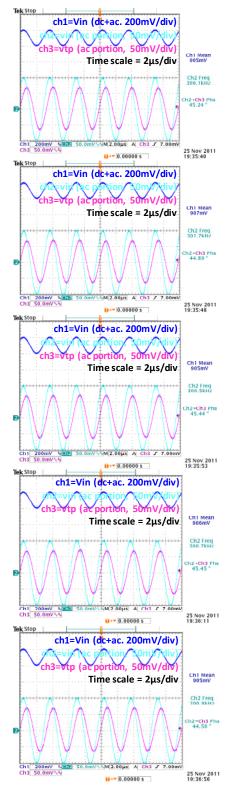

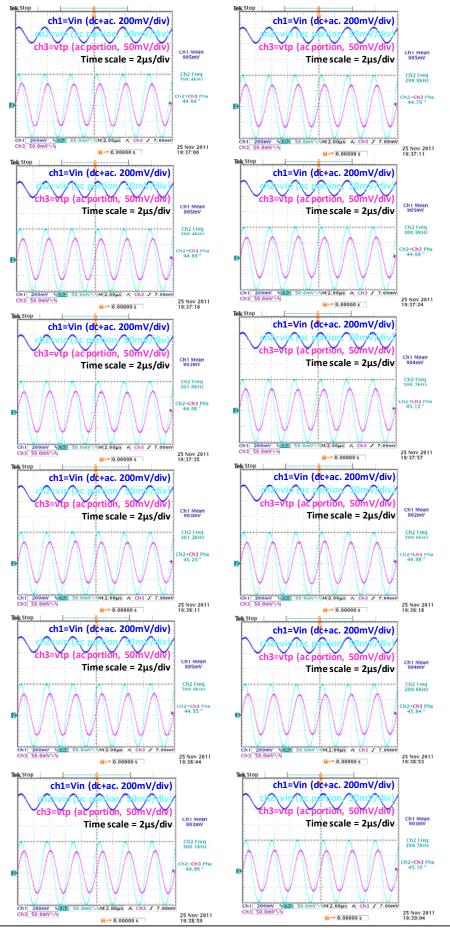

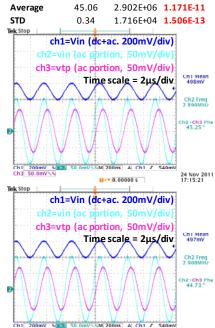

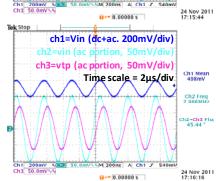

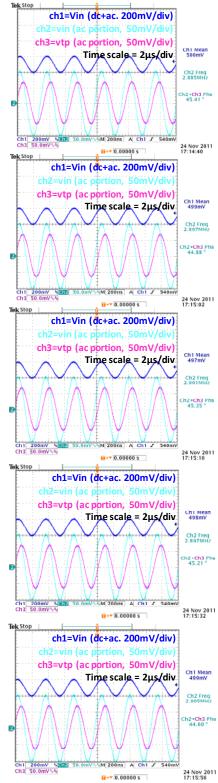

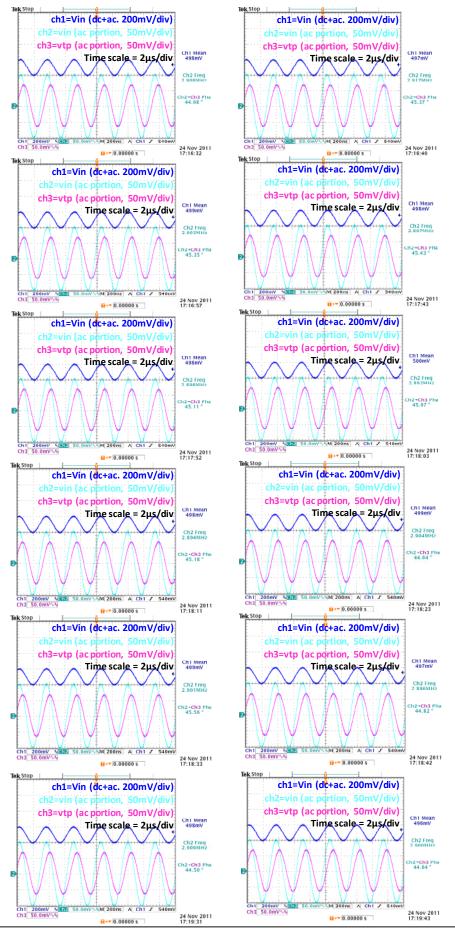

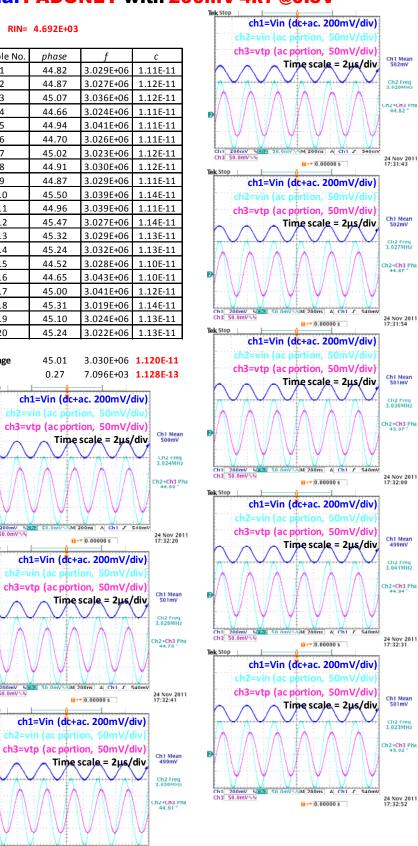

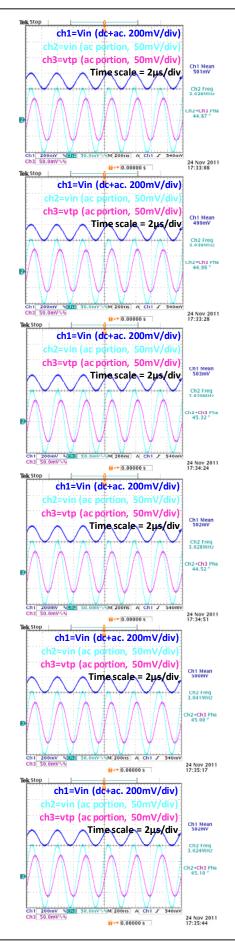

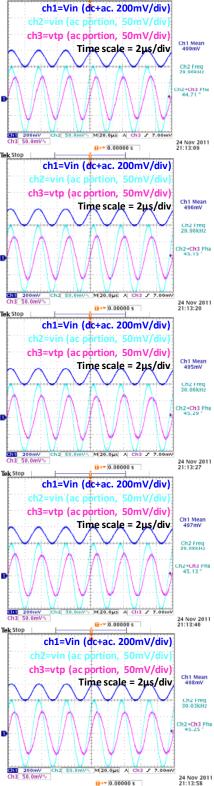

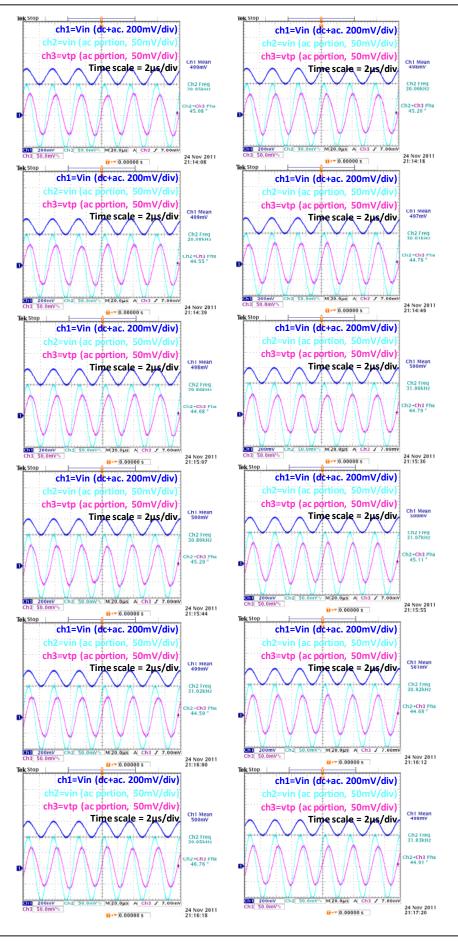

| $0.5V$ 106Figure 6-8 Postlayout Simulation Results of $C_{IN,eq}$ 107Figure 6-9 The microphotograph of the bulk-driven buffer presented in Section 6-1107107Figure 6-10 The Measurement Result of the Output Waveform with a 1Vp-p 10kHz108Sinusoidal Input108Figure 6-11 The Configured Setup for Determining the Input Capacitance of the Buffer |

| 0.5V                                                                                                                                                                                                                                                                                                                                               |

| $0.5V$ 106Figure 6-8 Postlayout Simulation Results of $C_{IN,eq}$ 107Figure 6-9 The microphotograph of the bulk-driven buffer presented in Section 6-1107107Figure 6-10 The Measurement Result of the Output Waveform with a 1Vp-p 10kHz108Sinusoidal Input108Figure 6-11 The Configured Setup for Determining the Input Capacitance of the Buffer |

| 0.5V                                                                                                                                                                                                                                                                                                                                               |

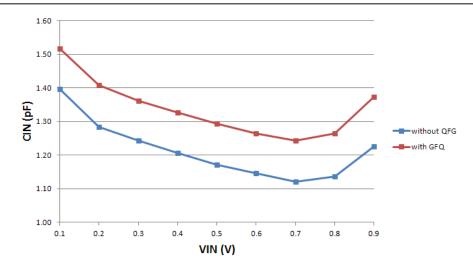

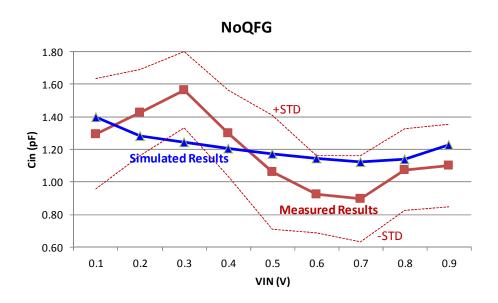

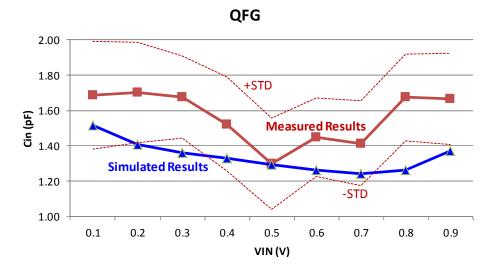

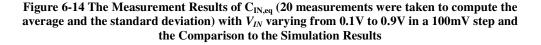

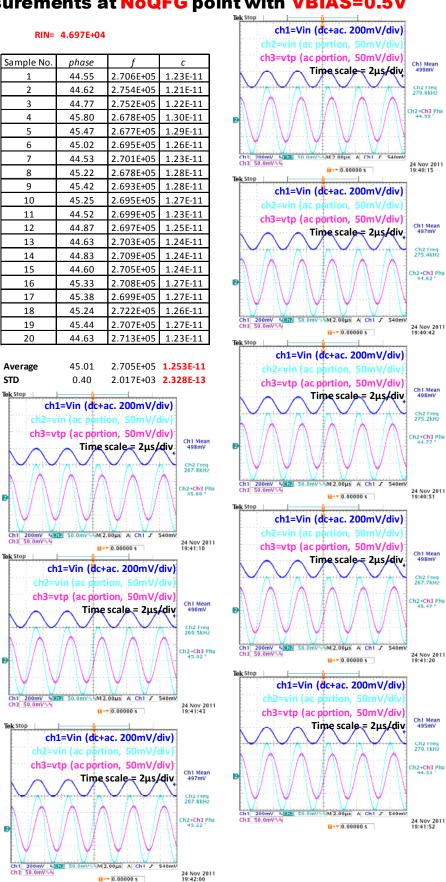

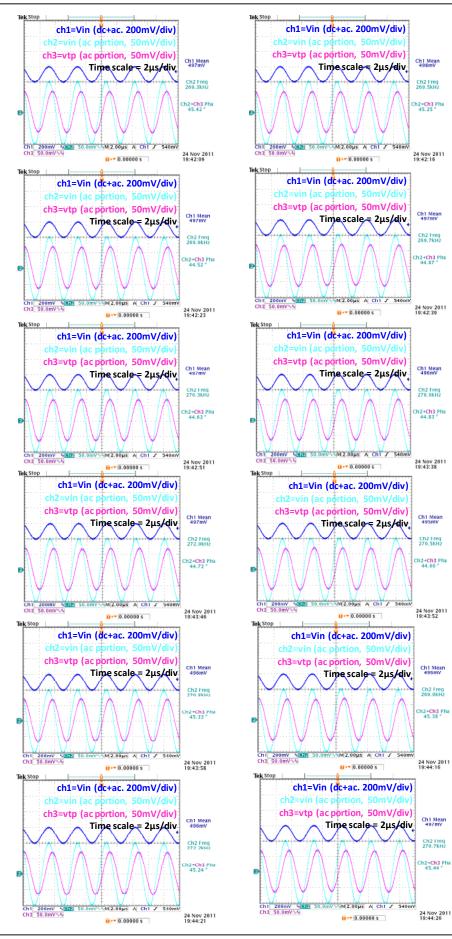

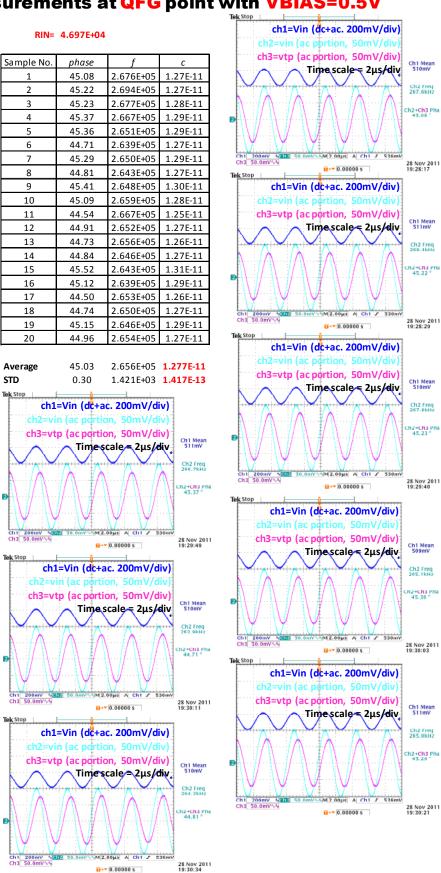

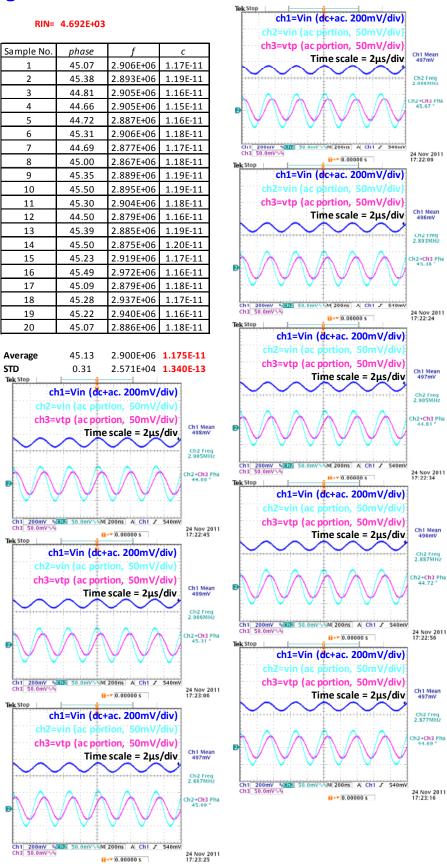

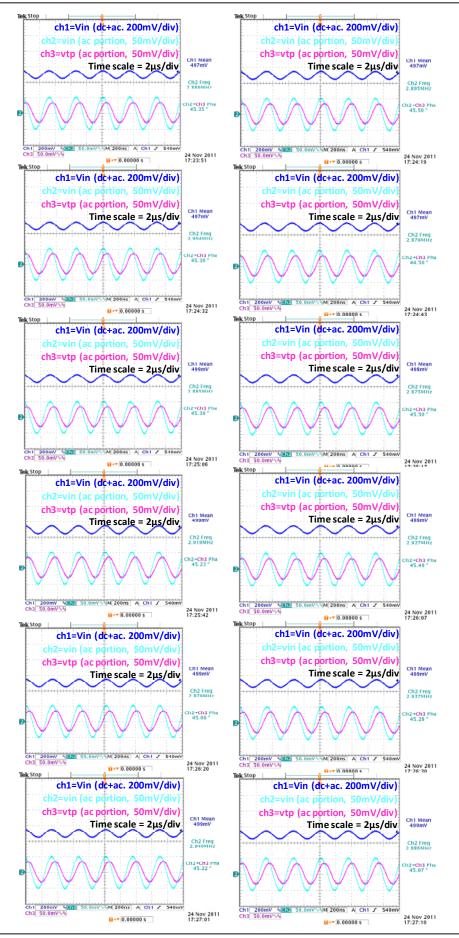

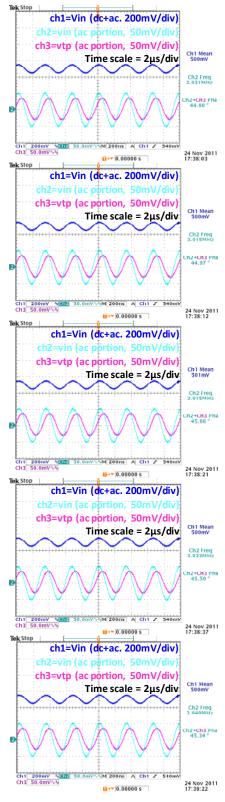

| Figure 6-14 The Measurement Results of $C_{IN,eq}$ (20 measurements were taken to       |      |

|-----------------------------------------------------------------------------------------|------|

| compute the average and the standard deviation) with $V_{IN}$ varying from 0.1V to 0.9V | in a |

| 100mV step and the Comparison to the Simulation Results                                 | 114  |

## List of Tables

| Table 3-1 Simulation Results of the Overall Performance of the Proposed Op-amp in       |

|-----------------------------------------------------------------------------------------|

| Figure 3-3                                                                              |

| Table 3-2 Simulated Results of the Overall Performance                                  |

| Table 4-1 Simulation Results of the Overall Performance of the Class AB DBFVF           |

| Circuit of Figure 4-4                                                                   |

| Table 4-2 Simulated results of the overall performance of Figure 4-14                   |

| Table 4-3 Simulated results of the overall performance of Figure 4-13(b) with different |

| level shift configurations                                                              |

| Table 4-4 Summary of the simulation results of Figure 4-23(a)                           |

| Table 5-1 Summary of the proposed OTA Performance                                       |

| Table 6-1 Device Dimensions for Figure 6-1    101                                       |

| Table 6-2 Measurement Results of Figure 6-12 with Various Resistance Values and the     |

| Amplitudes of the Test Signal111                                                        |

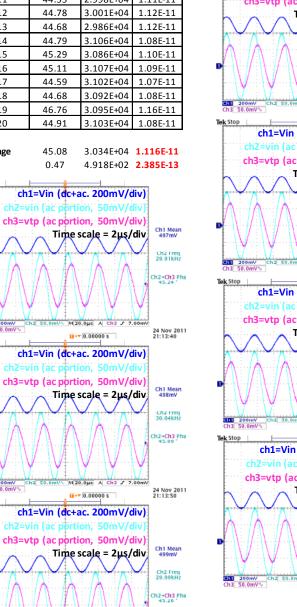

| Table C-1 Comparison of the Summary of the Measurement Results to the Simulation        |

| Results154                                                                              |

## List of Acronyms

| Name   | Definition                                    | Section defined |

|--------|-----------------------------------------------|-----------------|

|        |                                               |                 |

| BDCCM  | Bulk-Driven Cascoded Current Mirror           | 5.1.2           |

| BDDRB  | Bulk-Driven Double Replica-Biased             | 3.1.2           |

| BDDP   | Bulk-Driven Differential Pair                 | 3.1.1, 5        |

| BDFVDP | Bulk-Driven Flipped Voltage Differential Pair | 3.2.3           |

| BDFVF  | Bulk-Driven Flipped Voltage Follower          | 3.2.3, 4.1.3    |

| BDSSF  | Bulk-Driven Super Source Follower             | 4.2.2           |

| CMFB   | Common-Mode Feedback                          | 5.1.2           |

| FVF    | Flipped Voltage Follower                      | 4.1.1           |

| FVFDP  | Flipped Voltage Follower pseudo Differential  | 3.2.2           |

|        | Pair                                          |                 |

| GBW    | Gain-Bandwidth                                | 3.2.4           |

| ICMR   | Input Common-Mode Range                       | 2.1             |

| ITRS   | International Technology Roadmap for          | 1.1             |

|        | Semiconductor                                 |                 |

| JFET   | Junction Field Effect Transistor              | 2.1             |

| OTA    | Operational Transconductance Amplifiers       | 1.4, 3, 5       |

| PSRR   | Power Supply Rejection Ratio                  | 3.2.4, 5        |

| QFG    | Quasi-Floating Gate                           | 3.2.3, 4.2.2    |

| RBS    | Replica-Biased Scheme                         | 3.1.1           |

| SR     | Slew-Rate                                     | 3.1.1, 4.2.2    |

| SSF    | Super Source Follower                         | 4.2.1           |

| THD    | Total Harmonic Distortion                     | 4.1.4           |

## List of Symbols and Common MOSFET Equations

As this thesis consists of various equations with many symbols, the meaning of variables and physical constants are listed below so that readers can refer easily. Also, common MOSFET equations and a general note about the symbol convention are provided. [SED11], [JOH97], [ALL02], [BAK08], [GRA01]

#### List of Symbols

| Symbols used   | Description | Units |

|----------------|-------------|-------|

| in this thesis | Description | Omis  |

|                 | Physical constants                                                                      |         |

|-----------------|-----------------------------------------------------------------------------------------|---------|

| ε <sub>0</sub>  | Permittivity of free space = $8.854 \times 10^{-14}$ F/cm                               | F/cm    |

| ε <sub>Si</sub> | Permittivity of silicon = 11.7 $\varepsilon_0$ = 1.036 x 10 <sup>-12</sup> F/cm         | F/cm    |

| ε <sub>OX</sub> | Permittivity of SiO <sub>2</sub> = 3.97 $\varepsilon_0$ = 3.52 x 10 <sup>-13</sup> F/cm | F/cm    |

| k               | Boltzmann's constant = $1.38 \times 10^{-23} \text{ J/K}$                               | J/K     |

| q               | Charge of electron = $1.062 \times 10^{-19} \text{ C}$                                  | С       |

| $n_i$           | Intrinsic concentration of silicon = $1.45 \times 10^{10}$ /cm <sup>3</sup> at 300°K    | $/cm^3$ |

#### **Temperature parameters**

| Т              | Temperature in degree Kelvin = 300°K at room temperature                                                                                                                                                                                                     | K |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

|                | Thermal voltage (= 25.9mV at room temperature)                                                                                                                                                                                                               |   |

| V <sub>t</sub> | $V_t = \frac{kT}{q}$<br>Note: In this thesis, the thermal voltage is represented by $V_t$<br>(i.e. uppercase symbol with lowercase subscript), whereas<br>the threshold voltage is represented by $V_T$ (i.e. uppercase<br>symbol with uppercase subscript). | V |

|                   | Basic MOSFET parameters                                              |                  |

|-------------------|----------------------------------------------------------------------|------------------|

| 8m                | Transconductance of a gate-driven MOSFET                             | $\Omega^{-1}$    |

| 8mb               | Transconductance of a bulk-driven MOSFET                             |                  |

| g <sub>d</sub>    | Transconductance seen from the drain of a MOSFET                     | $\Omega^{-1}$    |

| t <sub>ox</sub>   | Gate-oxide thickness (SPICE parameter = TOX)                         | m                |

|                   | Gate-oxide thickness (SPICE parameter = TOX)                         | $\mathbf{r}$     |

| C <sub>ox</sub>   | $C_{OX} = \frac{\varepsilon_{OX}}{t_{OX}}$                           | F/m <sup>2</sup> |

| μ                 | Carrier mobility (SPICE parameter = U0)                              | $cm^2/V \cdot s$ |

| λ                 | Channel-length modulation coefficient (SPICE parameter = LAMBDA)     | V <sup>-1</sup>  |

|                   | Threshold voltage parameters                                         |                  |

| $V_{T0}$          | Zero-bias threshold voltage (SPICE parameter = VT0)                  | V                |

|                   | Substrate doping (SPICE parameter = NSUB)                            |                  |

| $N_A, N_D$        | $N_A$ = Number of acceptors in the p-type semiconductor              | /cm <sup>3</sup> |

|                   | $N_D$ = Number of donors in the n-type semiconductor                 |                  |

|                   | $\gamma = \frac{\sqrt{2q\varepsilon_{si}N_A}}{C_{ox}}$               |                  |

|                   | = body-effect coefficient (or bulk-threshold) of p-type              |                  |

|                   | semiconductor                                                        |                  |

| γ                 | $\gamma = \frac{\sqrt{2q\varepsilon_{si}N_D}}{C_{OX}}$               | V <sup>1/2</sup> |

|                   | = body-effect coefficient (or bulk-threshold) of n-type              |                  |

|                   | semiconductor                                                        |                  |

|                   | (SPICE parameter = GAMMA)                                            |                  |

|                   | $2 \Phi_{\rm F}  = -V_t \ln (N_A/n_i) =$ Fermi potential of a p-type |                  |

|                   | semiconductor                                                        |                  |

| $2 \Phi_{\rm F} $ | $2 \Phi_{\rm F}  = V_t \ln (N_D/n_i) =$ Fermi potential of an n-type | V                |

|                   | semiconductor                                                        |                  |

|                   | (SPICE parameter = PHI)                                              |                  |

|            | MOSFET Diode Parameters                                      |                  |

|------------|--------------------------------------------------------------|------------------|

| $I_S$      | Body-junction saturation current density (SPICE parameter    | $A/m^2$          |

|            | = JS)                                                        | A/III            |

| C          | Zero-bias body-junction capacitance, per unit area over the  | F/m <sup>2</sup> |

| $C_{J0}$   | drain/source region (SPICE parameter = CJ)                   | Г/Ш              |

| МТ         | Grading coefficient, for area component (SPICE parameter     |                  |

| MJ         | = MJ)                                                        |                  |

|            | Zero-bias body-junction capacitance, per unit length         |                  |

| $C_{JSW0}$ | alongF/m the sidewall (periphery) of the drain/source region | F/m              |

|            | (SPICE parameter = CJSW)                                     |                  |

| MICW       | Grading coefficient, for sidewall component (SPICE           |                  |

| MJSW       | parameter = MJSW)                                            |                  |

|            | Built-in voltage of an open-circuit pn junction, also known  |                  |

| $V_0$      | as bulk junction potential or barrier potential (SPICE       |                  |

|            | parameter = PB)                                              | V                |

|            | $V_0 = V_t \ln(\frac{N_A N_D}{n_i^2})$                       |                  |

### **MOSFET Dimension Parameters**

| AS, AD | Areas for source and drain (SPICE parameter = AS, AD) | $m^2$ |

|--------|-------------------------------------------------------|-------|

| PS, PD | Perimeters for source and drain                       | m     |

|        | (SPICE parameter = PS, PD)                            | m     |

### **MOSFET Gate-Capacitance Parameter**

| Cara      | Gate-source overlap capacitance, per unit channel width | F/m   |

|-----------|---------------------------------------------------------|-------|

| $C_{GSO}$ | (SPICE parameter = CGSO)                                | 17111 |

## **MOSFET Equations**

### Large-signal operation

|                | Linear Region                                                                   | Saturated Region                                                                        |

|----------------|---------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| ID             | $I_{D} = \mu_{0} C_{OX} \frac{W}{L} (V_{GS} - V_{T} - \frac{V_{DS}}{2}) V_{DS}$ | $I_{D} = \frac{\mu_{0}C_{OX}}{2} \frac{W}{L} (V_{GS} - V_{T})^{2} (1 + \lambda V_{DS})$ |

| V <sub>T</sub> | $V_T = V_{T0} + \gamma(\sqrt{2 \Phi})$                                          | $\frac{1}{ F  + v_{SB}} - \sqrt{2 \Phi_F })$                                            |

### Small-signal operation

|                                                 | Linear Region                                                                                           | Saturated Region                                                                                                             |

|-------------------------------------------------|---------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

| $g_m = \frac{\partial i_d}{\partial v_{gs}}$    | $\beta V_{DS} = \mu_0 C_{OX} \frac{W}{L} V_{DS}$                                                        | $\mu_0 C_{OX} \frac{W}{L} (V_{GS} - V_T) (1 + \lambda V_{DS})$ $= \sqrt{2\mu_0 C_{OX} \frac{W}{L} I_D (1 + \lambda V_{DS})}$ |

| $g_{mb} = \frac{\partial i_d}{\partial v_{bs}}$ | $\eta g_m = g_m \frac{1}{2\sqrt{2}}$                                                                    | $\frac{\gamma}{\sqrt{2 \Phi_F  + V_{SB}}}$                                                                                   |

| $g_d = \frac{\partial i_d}{\partial v_{ds}}$    | $\beta(V_{GS}-V_T-V_{DS})$                                                                              | $I_D \lambda$                                                                                                                |

| $C_{gs}$                                        | $C_{gs} = \frac{2}{3}WLC_{OX} + WC_{GSO}$                                                               |                                                                                                                              |

| $C_{bd}$                                        | $\frac{C_{j0}}{(1 - \frac{V_{BS}}{V_0})^{MJ}}AS + \frac{C_{jSW0}}{(1 - \frac{V_{BS}}{V_0})^{MJSW}}PS$   |                                                                                                                              |

| $C_{ds}$                                        | $\frac{C_{j0}}{(1 - \frac{V_{BD}}{V_0})^{MJ}} AS + \frac{C_{jSW0}}{(1 - \frac{V_{BD}}{V_0})^{MJSW}} PS$ |                                                                                                                              |

| $f_T$                                           | $\frac{g}{2\pi(C_{gs}+$                                                                                 | $\left(\frac{m}{C_{gd}}+C_{gb}\right)$                                                                                       |

### **Symbol Convention**

Unless otherwise stated, the following symbol convention is used to represent signals in this thesis:

| Represented Symbol                                                             | Meaning                                                                    |

|--------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| Uppercase symbols with<br>uppercase subscripts<br>(e.g. <i>I<sub>D</sub></i> ) | Bias or DC quantities<br>(e.g. the DC portion of transistor drain current) |

| Lowercase symbols with                                                         | Small-signal quantities                                                    |

| lowercase subscripts                                                           | (e.g. the incremental change in transistor drain                           |

| (e.g. $i_d$ )                                                                  | current)                                                                   |

| Lowercase symbols with                                                         | Sum of bias and small-signal quantities                                    |

| uppercase subscripts                                                           | (e.g. the total transistor drain current,                                  |

| (e.g. $i_D$ )                                                                  | i.e. $i_D = I_D + i_d$ )                                                   |

## Chapter 1 Introduction

#### 1.1 Moore's Law and More

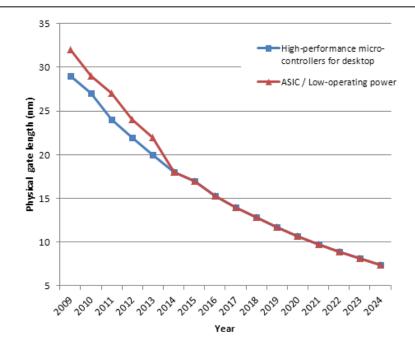

Complementary Metal-Oxide Semiconductor (CMOS) technology is continuously downscaling to increase the number of Metal-Oxide-Semiconductor Field Effect Transistors (MOSFET) to be integrated in a single chip. Intel co-founder Gordon E. Moore postulated the trend in 1965, which is known as Moore's Law, that the number of transistors per chip doubles roughly every 2 years [MOR65]. Along with this integration level trend, the cost-per-function is decreased and thus economic productivity and in effect overall quality of life are significantly improved through proliferation of computers, communication, and other industrial and consumer electronics [ITR10]. This miniaturisation trend, however, cannot be continued forever. Semiconductors are getting harder to downscale, and eventually the level of integration would not scale with Moore's Law anymore. Figure 1-1 shows how the International Technology Roadmap for Semiconductor (ITRS) draws the CMOS technology roadmap for the next decades.

Figure 1-1 CMOS Technology Roadmap [ITR10]

In order to keep up responding to the requirements in the economy growth and improving the quality of life despite the scaling limits according to Moore's Law which would come in the next decade, the ITRS has addressed a new concept of research target called "Moore's Law and More". This concept is constructed by three sub-sets of focus area - scaling, functional diversification, and beyond CMOS. Scaling (which is also known as more Moore) refers to not only the continued shrinking of transistors but also includes non-geometrical process techniques such as study of new materials that affect the electrical performance of the chip, as well as design technologies that enable high performance, low power, high reliability, low cost, and high design productivity. Functional diversification (which is also known as more than Moore) aims to provide additional value, in particular non-digital functionalities (e.g. RF communication), to be migrated from the system board level into package-level (system-in-package, SiP) or chip-level (System-on-Chip, SoC). Beyond CMOS focuses on a "new switch" that can provide substantial functional scaling beyond that attainable by ultimately scaled CMOS. In the field of Beyond *CMOS*, the ITRS lists some examples like carbon-based nano-electronics, spin-based

devices, ferromagnetic logic, atomic switches, and nano-electro-mechanical-system (NEMS) switches.

This CMOS technology trend introduces a new issue and consequently a motivation of new development in the area of CMOS analogue circuit design, which is described in the next section.

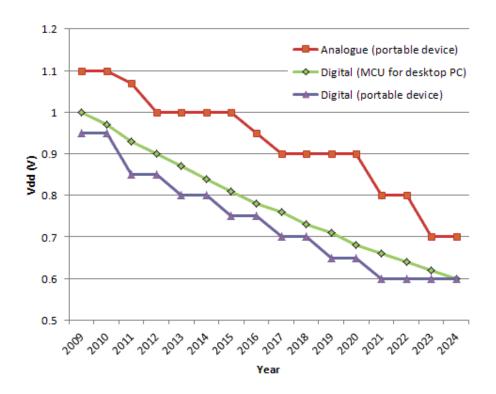

#### 1.2 Supply Voltage Trend

Along with the scaling trend of CMOS technology, the ITRS set the target of research effort towards lowering of supply voltages, since small transistors suffer from reduced voltage breakdowns (which is known as hot carrier effect) [ITR10]. Figure 1-2 shows how the ITRS draws the roadmap of supply voltage reduction for analogue and digital systems.

With Figure 1-2, the ITRS describes that the supply voltage reduction for analogue systems will continue to lag that of digital systems by two or more generations, due to the fact that the threshold voltage for CMOS technology is not expected to be decreased drastically. In digital systems, a threshold voltage too close to zero would cause appreciable leakage current to flow into logic devices even when they are off, which would result to increased power dissipation as the leakage current gets multiplied by the number of logic devices integrated in the digital system [ALL02]. Thus, from this reason the threshold voltage cannot be significantly reduced, which causes an issue from analogue circuit designers' viewpoint since conventional design techniques cannot fit into the ITRS roadmap. There is a need for new development of analogue circuit design techniques to overcome this dilemma.

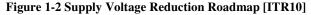

# 1.3 Rail-to-Rail Analogue Voltage Buffer and the Bulk-Driven Approach

One particular example where new circuit design techniques are needed for lowvoltage systems is analogue voltage buffers. Voltage buffers, which are usually constructed with an operational amplifier (op-amp) in unity-gain voltage configuration as illustrated in Figure 1-3(a), are essential building blocks for applications where the weak signal needs to be delivered to a large capacitive or a small resistive load without being distorted. In order to maximise the dynamic range under the low supply voltage constraint, rail-to-rail input and output stages are required for those op-amps.

Figure 1-3 (a) Op-amp in unity-gain configuration, (b) complementary differential pair, and (c) illustration describing dead-band region under low-supply voltage condition

For the input stage, the conventional circuit design approach for achieving rail-to-rail operation has been to utilise both p-type (pMOS) and n-type (nMOS) of the differential pairs as shown in Figure 1-3(b). However, as illustrated in Figure 1-3(c), the supply voltage being too low would cause a dead-band of the operational area where neither pMOS nor nMOS pairs can detect the input. In order to operate with this conventional circuit design approach, its supply voltage needs to be much greater than  $2V_T + 2V_{DSmin}$ , where  $V_T$  is the threshold voltage of the MOSFET and  $V_{DSmin}$ , is the minimum required voltage of drain-to-source voltage of the MOSFET. Considering that  $V_T$  varies by the bulk (or body) biasing voltage, the chip (or junction) temperature, and the process variation for the CMOS technology, a new circuit design approach such that the rail-to-rail operation can be achieved with a supply voltage near  $V_T$  is rather in favour for the ITRS roadmap.

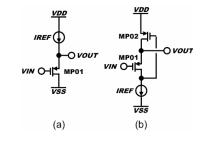

A candidate of circuit design techniques that can achieve rail-to-rail input operation with low supply voltages is the bulk-driven approach, which utilises the bulk of the MOSFET instead of the gate for applying the signal. Figure 1-4 illustrates this approach. With this technique the amount of supply voltage can be reduced to near  $V_T$ , however many drawbacks have been reported in [BLA98]. The author's research work solely focuses on the bulk-driven approach in order to develop new circuit design techniques that can overcome those drawbacks.

Figure 1-4 (a) pMOS bulk-driven device, and (b) nMOS bulk-driven device

#### 1.4 Research Objective and Thesis Outline

The research theme reported in this thesis is the bulk-driven approach. The research objective is to develop new circuit design techniques using the bulk-driven approach that can overcome many of those drawbacks which have been reported by literatures, and furthermore invent new ways application areas of the bulk-driven approach that can lead to performance enhancement in the field of CMOS analogue amplifier design. This thesis is structured as follows:

Chapter 2 provides a general overview of the bulk-driven approach. The device physics, operation principle and mathematical modelling, and drawbacks of this circuit design approach are discussed.

Chapter 3 focuses on the circuit design techniques of rail-to-rail input stage for analogue amplifiers using the bulk-driven approach. This chapter reviews previous works and proposes a novel new circuit design technique that solves the issues of nonlinearity and latch up. Furthermore, another new circuit design technique that can achieve low-power high-speed performances whilst minimise the issue of low-input resistance large input capacitance of the bulk-driven approach is also proposed.

Chapter 4 presents a new invention of designing source followers using the bulkdriven approach, which in author's best knowledge has not been proposed in literatures before. A new design technique of source followers such that the DC level shift can be freely programmed is proposed in this chapter.

Chapter 5 proposes a new way of utilising the bulk of the cascode devices at the output stage of Operational Transconductance Amplifiers (OTA), which leads to enhanced output resistance without having any additional hardware in the core part of the OTA.

Chapter 6 focuses on the study of the input capacitance of a bulk-driven buffer. To verify the use of the BSIM3 MOSFET model in the simulating for predicting the input capacitance, the measurement data of the fabricated device compared with the simulated results using the extracted netlist of the postlayout design.

Chapter 7 is the concluding session of this research work. The summary of this work and the author's recommendations for further work are provided.

Lastly, Appendix A provides the copies of the author's publications, Appendix B provides the supplementary information to Chapter 6 (including the SPICE code used for the simulation, the IC layout of the whole die and the bonding diagram, more snapshots of the microphotograph, and the used test board for the measurement), and Appendix C lists the logs of the measurement results of the input capacitance of the fabricated bulk-driven buffer presented in Chapter 6.

#### 1.5 List of the Author's Publications

The author's research works documented in this thesis are based on the following publications:

- [HAG05] Y. Haga, H. Zare-Hoseini, L. Berkovi, and I. Kale, "Design of a 0.8

Volt Fully Differential CMOS OTA Using the Bulk-Driven Technique", *IEEE Proc. International Symposium in Circuits and Systems*, 2005, pp. 220 – 223

- [HAG06] Y. Haga, R. C. S. Morling, and I. Kale, "A New Bulk-Driven Input Stage Design for sub 1-volt CMOS Op-Amps", *IEEE Proc. International Symposium in Circuits and Systems*, 2006, pp.1547 – 1550

- [HAG09A] Y. Haga and I. Kale, "Bulk-Driven Flipped Voltage Follower", IEEE Proc. International Symposium in Circuits and Systems, 2009, pp.2717 – 2720

- [HAG09B] Y. Haga and I. Kale, "CMOS Buffer Using Complementary Pair of Bulk-Driven Super Source Followers", *IEEE Electronic Letters*, Vol. 45, Issue 18, 2009, pp. 917 – 918

- [HAG09C] Y. Haga and I. Kale, "Class-AB Rail-to-Rail CMOS Buffer with Bulk-Driven Super Source Followers", *IEEE European Conference on Circuit Theory and Design*, 2009, pp. 695 – 698

- [HAG10] Y. Haga and I. Kale, "Bulk-Driven Flipped Differential Pair", *IEEEProc. PhD Research in Microelectronics and Electronics*, 2010

- [HAG11] Y. Haga and I. Kale, "Bulk-Driven DC Level Shifter", *IEEE Proc. International Symposium in Circuits and Systems*, 2011, pp.2039-2042

The knowledge contributions of the above publications are summarised in the next section.

#### 1.6 Knowledge Contributions

The work presented in this thesis, which includes several novel proposals of circuit design techniques that utilise the bulk-driven approach, is solely developed by the author. The novelties of these developed techniques, which greatly help enhancing performances in the CMOS analogue amplifier design field, are described below:

Applying the proposal at the input stage of CMOS analogue amplifiers not only leads to providing rail-to-rail operation at extremely low supply voltage condition, but also improves the linearity and furthermore enhances the latch up immunity [HAG06]. In fact there are several previously proposed works that improve the linearity of the bulk-driven approach, however in the author's best knowledge there is no publication of the technique that can enhance the latch up immunity.

This thesis also presents another input stage design technique utilising the bulkdriven approach, which achieves low-power high-speed performances and helps reducing the input capacitance [HAG10]. A new concept of utilising a reversedbiased diode with the bulk-driven MOSFET is introduced.

Applying the bulk-driven approach in source follower design is a complete new way of circuit design techniques. The bulk-driven approach allows the DC level shift to be freely programmed, which has not been possible to do with conventional source followers [HAG09A], [HAG09B], [HAG09C], [HAG11].

Utilising the bulk-driven approach in the cascode devices of the OTA is also a complete new design method, which leads to increasing the output resistance and hence enhancing the open-loop gain of the OTA without the need of any extra hardware in the core part of the OTA [HAG05].

With the above contributions to knowledge, the author aims to make for the readers of this thesis to realise that the bulk-driven approach has many new possible ways to be applied in CMOS analogue amplifier design for further performance improvement, and to encourage for new researchers to continue with developing modified techniques of the bulk-driven approach.

#### 1.7 Impact of this Work

This last section of the Chapter aims to demonstrate the impact of this research work.

During the research activities, the author noticed that the work reported in this thesis has been cited by several institutions' works. Section 1.7.1 shows the list of citations to the author's publications which the author is aware of.

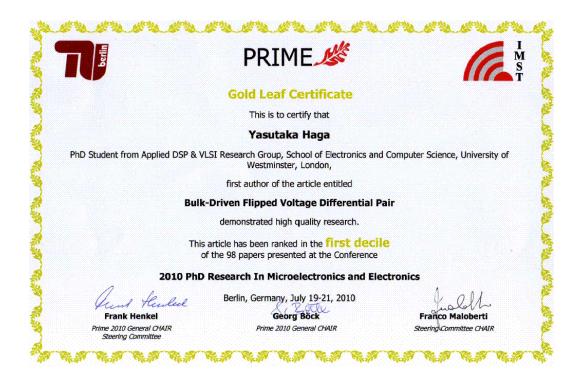

The BDFVDP reported in Chapter 3 of this thesis, which is the work the author published in [HAG10], received the Gold Leaf Certificate from PhD Research In Microelectronics and Electronics (PRIME). In Section 1.7.2, the scanned copy of the received award is shown.

#### 1.7.1 The List of "Referred" Publications

The List of Citations to [HAG05]

- [AGG09] B. Aggarwal and M. Gupta, "Low-Voltage Cascode Current Mirror based on Bulk-Driven MOSFET and FGMOS techniques", IEEE Proc. International Conference on Advances in Recent Technologies in Communication and Computing, 2009, pp. 474 – 477

- [BAU07] F. Bautista, S. O. Martínez, G. Dieck, and O. Rossettoy, "An ultralow voltage high gain operational transconductance amplifier for biomedical applications", Workshop on Design and Architectures for Signal and Image Processing (DASIP), 2007, Grenoble: France

- [CAR09] J. M. Carrillo, R. Pérez-Aloe, J. M. Valverde, and J. F. Duque-Carrillo, "Compact Low-Voltage Rail-to-Rail Bulk-Driven CMOS Opamp for Scaled Technologies", *IEEE Proc. European Conference* on Circuits Theory and Design, 2009, pp. 263 – 266

- [CAR10] J. M. Carrillo, G. Torelli, R. Pérez-Aloe, J. M. Valverde, and J. F. Duque-Carrillo, "Single-pair bulk-driven CMOS input stage: A compact low-voltage analog cell for scaled technologies" *Integration, the VLSI Journal*, 2010, Vol.43, Issue 3, pp. 251 – 257, Elsevier

- [CAR11] J. M. Carrillo, G. Torelli, M. A. Domínguez, and J. F. Duque-Carrillo, "On the input common-mode voltage range of CMOS bulkdriven input stages", *International Journal of Circuit Theory and Applications*, 2011, 39, pp. 649 – 664, Wiley Online Library

- [CHA10] C. Chanapromma and K. Daoden, "A CMOS Fully Differential Operational Transconductance Amplifier Operating in Sub-threshold Region and Its Application", *IEEE Proc. International Conference* on Signal Processing Systems, 2010, pp. V2-73 – V2-77

- [HE06] X-Y He, K-P Pun, C-S Choy, and C-F Chan, "A 0.5V Fully Differential OTA with Local Common Feedback", *IEEE Proc. International Symposium on Circuits and Systems*, 2006, pp. 1559 – 1562

- [KHA10] H. Khameh and H. Shamsi, "A Sub-1V High-Gain Two-Stage OTA Using Bulk-Driven and Positive Feedback Techniques", *IEEE Proc. European Conference on Circuits and Systems for Communications*, 2010, pp. 103 – 106

- [LAY08] K. D. Layton, D. T. Corner, and D. J. Corner, "Bulk-driven gainenhanced fully-differential amplifier for VT + 2Vdsat operation", *IEEE Proc. International Symposium on Circuits and Systems*, 2008, pp. 77 – 80

- [LI10] Y. Li, C. C. Y. Poon, and Y-T Zhang, "Analog Integrated Circuits Design for Processing Physiological Signals", *IEEE Reviews in Biomedical Engineering*, 2010, Vol. 3, pp. 93 – 105

- [PAN09] S-W Pan C-C Chuang C-H Yang and Y-S Lai, "A novel OTA with dual bulk-driven input stage", IEEE Proc. International Symposium on Circuits and Systems, 2009, pp. 2721 – 2724

- [RAI10] G. Raikos and S. Vlassis, "0.8 V Bulk-Driven Operational Amplifier", Analog Integrated Circuits and Signal Processing, 2010, 63, pp. 425 – 432, Springer

- [ROH10] H. Roh, H. Lee, Y. Choi, and J. Roh, "A 0.8-V 816-nW delta-sigma modulator for low-power biomedical applications", Analog Integrated Circuits and Signal Processing, 2010, 63, pp. 101 – 106, Springer

- [TAI06] C-F Tai, J-L Lai, and R-J Chen, "Using Bulk-driven Technology

Operate in Subthreshold Region to Design a Low Voltage and Low Current Operational Amplifier", *IEEE Proc. International Symposium on Consumer Electronics*, 2006, pp. 1 – 5

[ZAB07] S. A. Zabihian, and R. Lotfi, "Ultra-Low-Voltage, Low-Power, High-Speed Operational Amplifiers Using Body-Driven Gain-Boosting Technique", IEEE Proc. International Symposium on Circuits and Systems, 2007, pp. 705 – 708

The List of Citations to [HAG06]

- [CAR11] J. M. Carrillo, G. Torelli, R. Pérez-Aloe, J. M. Valverde, and J. F. Duque-Carrillo, "On the input common-mode voltage range of CMOS bulk-driven input stages", *International Journal of Circuit Theory and Applications*, 2011, 39, pp. 649 664, Wiley Online Library

- [LI10] Y. Li, C. C. Y. Poon, and Y-T Zhang, "Analog Integrated Circuits Design for Processing Physiological Signals", *IEEE Reviews in Biomedical Engineering*, 2010, Vol. 3, pp. 93 – 105

- [RAI10] G. Raikos and S. Vlassis, "0.8 V Bulk-Driven Operational Amplifier", Analog Integrated Circuits and Signal Processing, 2010, 63, pp. 425 – 432, Springer

The List of Citations to [HAG09A]

[KHA11] F. Khateb, N. Khatib, and D. Kubánek, "Novel low-voltage lowpower high-precision CCII± based on bulk-driven folded cascade OTA", Microelectronics Journal, 2011, 42, pp. 622 - 631, Elsevier

- [RAI10] G. Raikos and S. Vlassis, "0.8 V Bulk-Driven Operational Amplifier", Analog Integrated Circuits and Signal Processing, 2010, 63, pp. 425 – 432, Springer

- [YOD10] A. Yodtean, P. Isarasena, and A. Thanachayanont, "0.8-µW CMOS Bulk-Driven Linear Operational Transconductance Amplifier in 0.35-µm Technology", *IEEE Proc. Asia Pacific Conference on Circuits and Systems*, 2010, pp. 784 – 787

The List of Citations to [HAG09B]

[URB11] C. Urban, J. E. Moon, and P.R. Mukund, "Scaling the Bulk-Driven MOSFET into Deca-Nanometer Bulk CMOS Processes", *Microelectronics Reliability Journal*, 2011, 51, pp. 727 – 732, Elsevier

The List of Citations to [HAG09C]

- [KUM11] M. Kumar and G. Kumar, "Optimization Techniques for Source Follower Based Track-and-Hold Circuit for Wireless High Speed Wireless Communication", AIRCC International Journal of VLSI design & Communication Systems, 2011, Vol.2, No. 1, pp. 45 – 59

- [MAR11] A. L. Martin, J. M. A. Miguel, L. Acosta, J. Ramírez-Angulo, and R.

G. Carvajal, "Design of Two-Stage Class AB CMOS Buffers: A Systematic Approach", *ETRI Journal*, 2011, Vol.33, No.3, pp. 393 400

1.7.2 The Scanned Copy of the Gold Leaf Certificate Awarded by PRIME'10

# Chapter 2 Characterising the Bulk-Driven Approach

This chapter provides an overview of the bulk-driven approach, which is essential to be understood in prior to assessing the bulk-driven circuit design. The benefit of the bulk-driven approach, the device realisation in CMOS technology, and the drawbacks are thoroughly discussed.

## 2.1 The Benefit of Utilising the Bulk-Driven Approach

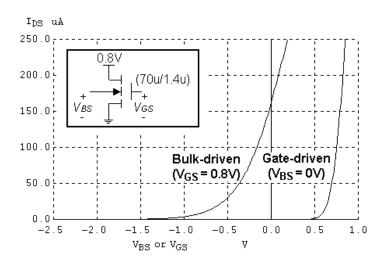

The benefit of the bulk-driven approach can be easily realised by simulating its transconductance characteristics and comparing with the gate-driven approach. Figure 2-1 shows the simulated plot of the gate-driven and the bulk-driven nMOS transistors using a 0.35µm CMOS technology.

Figure 2-1 Simulating transconductance characteristics of gate-driven and bulk-driven nMOS transistors using a 0.35µm CMOS technology

As can be seen in Figure 2-1, to operate the gate-driven MOS transistor in the active region, the gate-to-source voltage needs to be greater than the threshold voltage (which is approximately 0.6 volts in this case). On the other hand, the bulk-driven MOS transistor behaves in a similar fashion to a depletion MOS transistor or a Junction Field Effect Transistor (JFET). Therefore, with the zero-bias voltage at the input node, the transistor is still in the active region.

This characteristic is the key benefit we use in designing low-supply voltage opamps and other analogue circuits, as the bulk-driven device allows an extension in its input range on the negative side and hence leads to improving the Input Common-Mode Range (ICMR).

## 2.2 Realising the Bulk-Driven Device in CMOS Technology

This section describes how a bulk-driven device is realised in CMOS technology, which is an important topic to be covered before discussing the drawbacks of the bulk-driven approach. Case studies of the realisation in n-well type and in twin-well type of CMOS technologies are discussed.

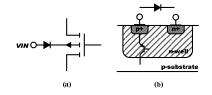

#### 2.1.1 Bulk-Driven Device Realised in N-Well CMOS Technology

In semiconductor market today n-well CMOS technologies are more popular than pwell types, since n-types ones allows the substrate to be connected to the ground instead of the supply voltage, which is in more favour by circuit designers [SAN06], [YTT03]. Thus, it is essential to discuss the realisation of a bulk-driven device in nwell CMOS technology. In n-well CMOS technology, pMOS can be bulk-driven. Figure 2-2 illustrates the cross sectional view of how the pMOS bulk-driven device can be realised in an n-well CMOS technology.

Figure 2-2 Cross sectional view of a bulk-driven pMOS device in an n-well CMOS technology

The operation principle of a bulk-driven device is simple to follow. The voltage at the bulk affects the depletion region depicted in Figure 2-2, which in effect controls the channel and hence the drain current. Let's suppose that the pMOS device formed in the n-well in Figure 2-2 is in linear region, and thus the depth of the p-type channel is narrower at the drain than the source, as shown in the sketch. As the voltage potential at the bulk of the pMOS device is increased above the source, the depletion region becomes widened and hence the p-type channel reduces its overall depth, and eventually the channel is pinched off at the drain end so that the pMOS device becomes saturated [ALL02].

The behaviour of the reduced channel depth can be alternatively described that the overvoltage of the pMOS device is decreased when the bulk voltage increases above the source voltage  $V_{SB}$  [SED11]. However, since the gate voltage of the pMOS

device  $V_{SG}$  remained unchanged, the threshold voltage  $V_T$  increased instead. This  $V_T$  behaviour can be mathematically modelled by:

$$V_{T} = V_{T0} + \gamma(\sqrt{2|\Phi_{F}| + V_{SB}} - \sqrt{2|\Phi_{F}|})$$

(2-1)

where  $V_{T0}$  is the threshold voltage at zero-bias (i.e.  $V_{SB}=0$ ),  $\gamma$  is the body-effect coefficient, and  $2|\Phi_{\rm F}|$  is the Fermi potential, which are all dependent of the CMOS technology. Hence in summary, with the bulk-driven approach the drain current is controlled by varying  $V_T$  instead of  $V_{SG}$ .

From Figure 2-2 it is important to realise the parasitic bipolar effect, which are denoted as QP and QV in the sketch, since this parasitic effect contributes to one of the severe drawbacks of the bulk-driven approach. More detail discussions of this drawback is covered in Section 2.3.

Finally, it is worth adding a comment that a bulk-driven transistor is often said to be in *depleted-mode* [BLA96] since the voltage potential at the bulk affects the shape of the depletion region. However, in terms of device physics the actual MOS transistor that is dealt with is enhancement type, thus this discussion may cause confusion by first-time learners of the bulk-driven approach.

#### 2.1.2 Bulk-Driven Device Realised in Twin-Well CMOS Technology

Since twin-well CMOS technology is also available today, it is also worth discussing how a bulk-driven device can be realised in this technology. The cross section view is sketched in Figure 2-3.

Figure 2-3 Cross sectional view of twin-well CMOS technology

In the previous section it was discussed that only pMOS can be bulk-driven in n-well technology. In twin-well technology, on the other hand, nMOS device can also be bulk-driven since the device has an isolated body (bulk) in p-well instead of the common p-substrate.

As can be observed from Figure 2-3, the parasitic bipolar effect for the pMOS formed in twin-well technology remains in identical manner as the pMOS device formed in n-well technology. This is because, in either case, the n-well is formed in p-substrate. In contrast, with the nMOS there is only one type of bipolar effect denoted by QN. This is because p-well and p-substrate are not related by pn-junction effect since they both have the p-type of polarity.

It is worth noting that this technology allows separate optimization of the nMOS and pMOS transistors [SED11], and therefore many submicron processes are based on this technology. As mentioned before, with this technology both pMOS and nMOS devices can be bulk-driven. However for fabless semiconductor companies where the fabrication needs to be outsourced, there might be a case that the foundry allows layout designers to draw only n-well layers but not p-well layers [MOS11], which consequentially means that layout designers cannot assign nMOS devices to be

individually bulk-driven. This matter has to be identified before starting the circuit design.

## 2.3 Drawbacks Introduced with the Bulk-Driven Approach

In Section 2.1 the benefit of the bulk-driven approach has been described that the transistor can be utilised in depleted-mode similar like JFET. However, many associated drawbacks have been reported in [BLA98]. This section thoroughly discusses these drawbacks, as they are essential to be understood in prior to assessing the bulk-driven circuit design.

## 2.3.1 Transconductance Reduction

One significant disadvantage of the bulk-driven approach is that the transconductance of a bulk-driven MOSFET  $g_{mb}$  is substantially less than a gatedriven MOSFET  $g_m$ . As can be realised from Figure 2-1, the slope of the bulk-driven MOSFET (=  $g_{mb}$ ) is much gentle than the slope of the gate-driven MOSFET (=  $g_m$ ). The  $g_{mb}/g_m$  ratio,  $\eta$ , can be expressed by

$$\eta = g_{mb} / g_m = \frac{\gamma}{2\sqrt{2|\Phi_F| - V_{BS}}}$$

(2-2)

where  $2|\Phi_{\rm F}|$  is the Fermi potential,  $\gamma$  is the body-effect coefficient, and  $V_{BS}$  is the bulk-to-source voltage of the MOSFET. This ratio  $\eta$  is thus dependent to  $V_{BS}$ , but it is typically around 0.1 to 0.3 [SED11].

#### 2.3.2 Transconductance Variation

It can be also noted from Equation (2-2) that  $g_{mb}$  (=  $\eta g_m$ ) is dependent to  $V_{BS}$ , which causes a substantial transconductance variation when a bulk-driven MOSFET is applied in a differential pair design.

## 2.3.3 Process Related

As discussed in Section 2.2, the polarity of the bulk-driven MOS transistor is process related because *wells* are required to isolate bulk-terminals. In case of n-well CMOS technology, only pMOS devices can be bulk-driven. For applications where both pMOS and nMOS devices are required, a twin-well technology is needed.

## 2.3.4 Degraded Latch up Immunity

As can be observed from Figure 2-2 and 2-3, CMOS technologies consist of parasitic bipolars. If for instance any of those bipolars, in particular vertical bipolars QV, are turned on, then there would be a short-circuit path between positive and negative supply rails. In digital systems this is known as a latch up effect, which may cause destructive breakdown of the chip.

To minimise this unwanted effect to happen, the forward-bias voltage of the bulk of the MOSFET must be kept as small as possible in order not to strongly turn on the parasitic bipolars [BLA98].

#### 2.3.5 Degraded Input Impedance Characteristics

With the bulk-driven approach, the input impedance characteristics become worse due to the parasitic bipolars. The resistive and input capacitive characteristics of the bulk-driven input are thoroughly discussed below:

#### Input Resistance

As illustrated in Figure 2-2, the bulk of the MOSFET is the base terminal of the parasitic bipolar. Therefore some appreciable input current  $i_B$  may flow.  $i_B$  can be expressed by

$$i_B = I_S[\exp(\frac{qv_{BS}}{kT}) - 1]$$

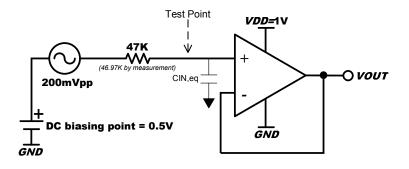

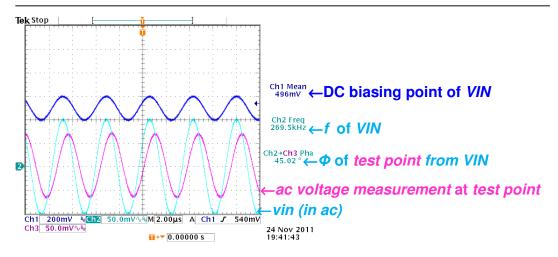

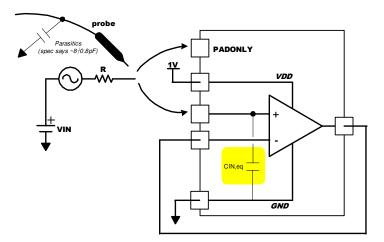

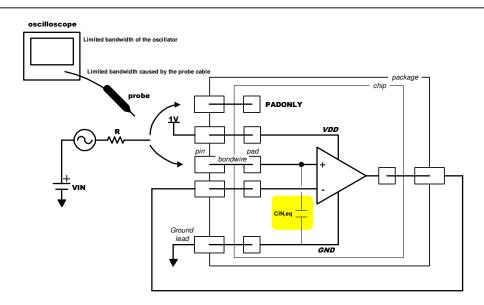

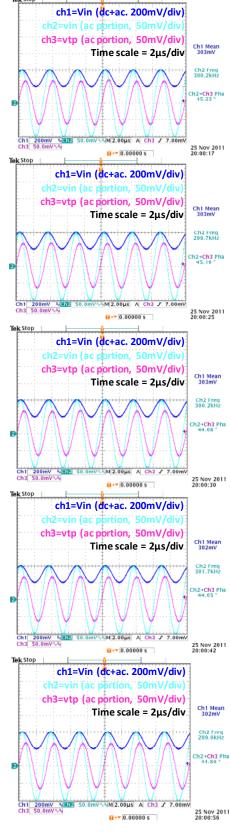

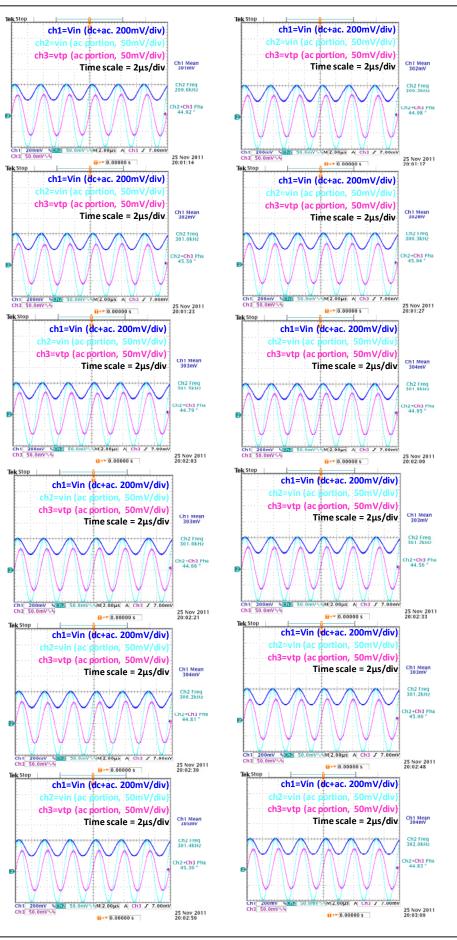

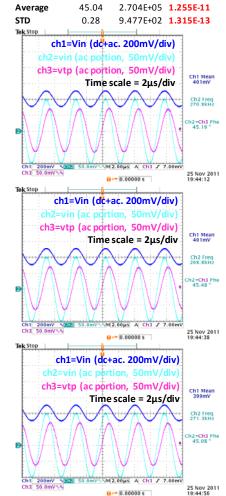

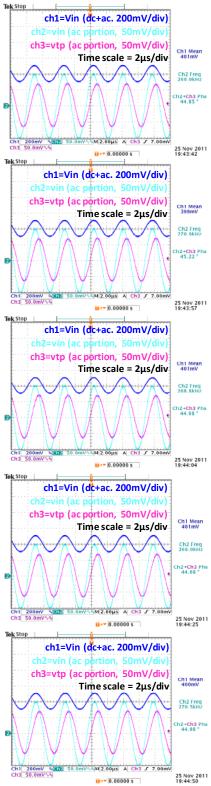

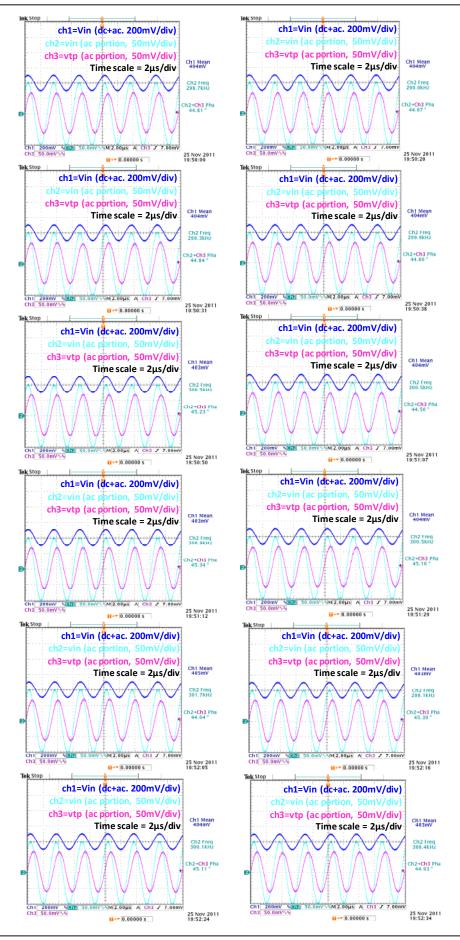

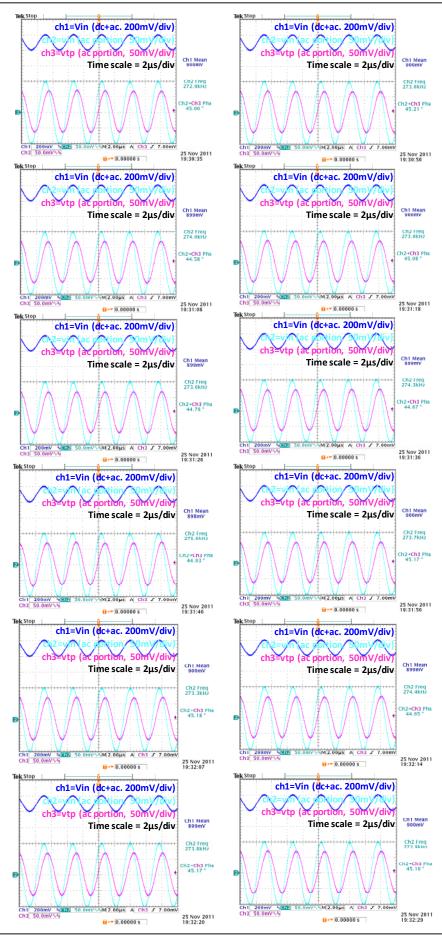

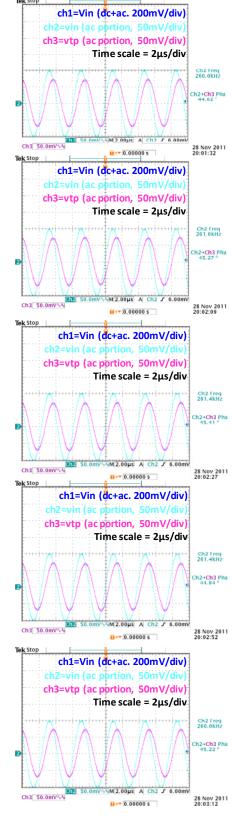

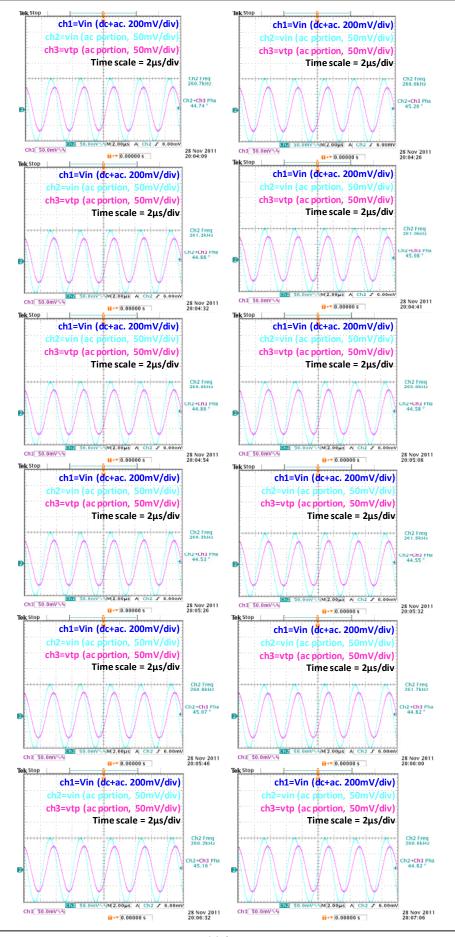

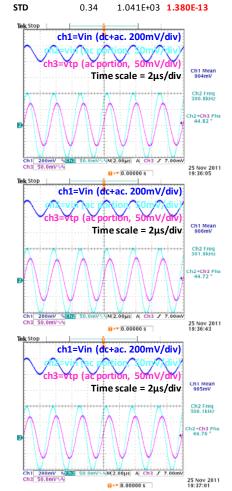

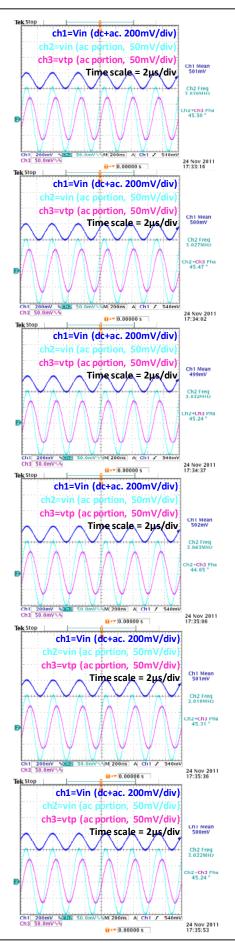

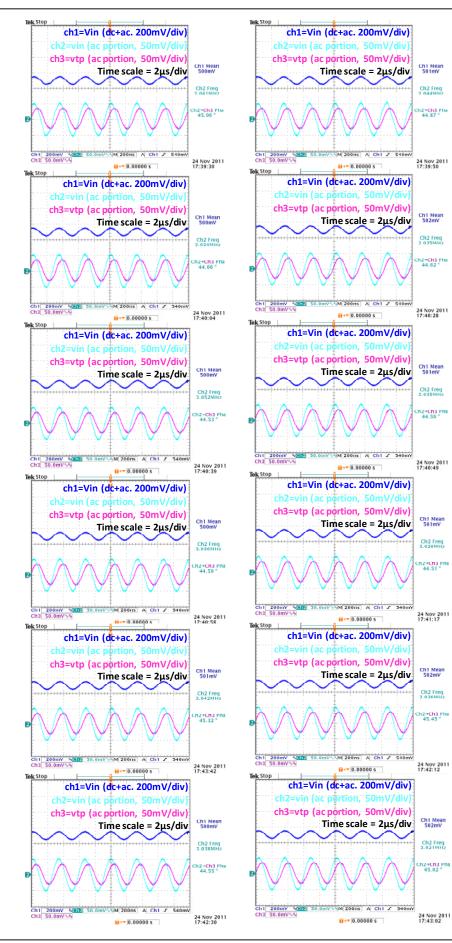

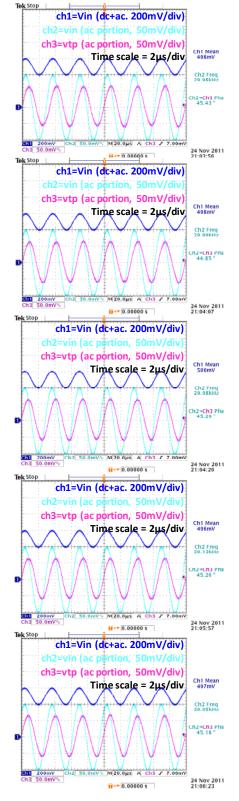

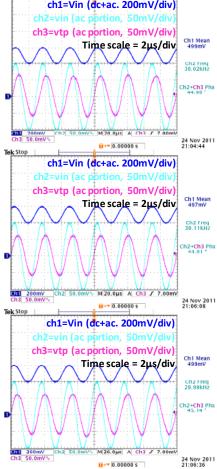

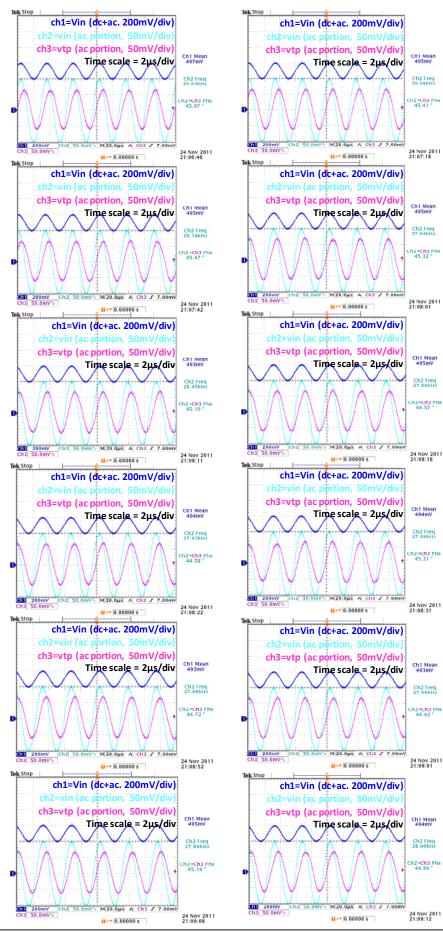

(2-3)